Приложение А.

Системотехника

IBM PC-совместимых

компьютеров

Здесь рассмотрено взаимодействие программ с интерфейс-

ными адаптерами. Приведены краткие сведения по архитек-

туре PC. Описаны организация пространств памяти и вво-

да/вывода, система прерываний и прямой доступ к памяти.

Более подробные сведения можно найти в книге "Аппарат-

ные средства IBM PC. Энциклопедия" ("Питер", 1998).

А.1. Пространство памяти

Логическая структура памяти PC обусловлена системой ад-

ресации процессоров семейства х86. Процессоры 8086/88,

применявшиеся в первых моделях IBM PC, имели адресное

пространство 1 Мбайт (20 бит шины адреса). Начиная с про-

цессора 80286 шина адреса была расширена до 24 бит, затем

(386DX, 486, Pentium) до 32 и, наконец, до 36 бит

(Pentium Pro, Pentium II). В реальном режиме процессора,

используемом в DOS, формально доступен лишь 1 Мбайт

памяти. Однако из-за ошибки эмуляции процессора 8086 в

реальном режиме процессоры 80286 и выше имеют макси-

мально доступный адрес lOFFEFh, что на (64К-16) байт

больше. Область lOOOOOh-lOFFEFh называется высокой па-

мятью - High Memory Area (HMA). В нее помещают часть

ОС реального режима и небольшие резидентные програм-

мы. Для полной совместимости с процессором 8086/88 име-

ется вентиль линии А20 шины адреса - GateA20, который

либо пропускает сигнал от процессора, либо принудительно

обнуляет линию А20 системной шины адреса.

Основную часть адресного пространства занимает оператив-

ная память. Объем установленной памяти определяется те-

стом POST при включении компьютера, начиная с младших

адресов. Натолкнувшись на отсутствие памяти (ошибку), тест

останавливается и сообщает системе объем памяти.

Память, непосредственно адресуемая процессором, распре-

деляется следующим образом:

^ OOOOOh-9FFFFh - Conventional {Base) Memory,

640 Кбайт - стандартная (базовая) память, доступная

DOS и программам реального режима. В некоторых сис-

темах с видеоадаптером MDA верхняя граница сдвигает-

ся к AFFFFh (704 Кбайт). Иногда верхние 128 Кбайт

стандартной памяти (область 80000h-9FFFFh) называют

Extended Conventional Memory.

^ AOOOOh-FFFFFh - Upper Memory Area (UMA),

384 Кбайт - верхняя память, зарезервированная для си-

стемных нужд. В ней размещаются буферы интерфейс-

ных адаптеров (например, видеопамять) и постоянная

память (BIOS с расширениями).

^ Память выше lOOOOOh - Extended Memory -дополнитель-

ная (расширенная) память, непосредственно доступная

только в защищенном режиме компьютеров 286 и выше.

Для компьютеров класса AT с 24-битной шиной адреса верх-

няя граница дополнительной памяти - FDFFFFh (макси-

мальный размер 14,9 Мбайт). Область FEOOOOh-FFFFFFh

содержит ПЗУ BIOS (ROM BIOS Area); обращение к ней

эквивалентно обращению к ROM BIOS по адресам OEOOOOh-

OFFFFFh.

Для процессоров 386 и 32-битной шины адреса теоретичес-

кая верхняя граница - 4 Гбайт, а для Pentium Pro и

Pentium II-64 Гбайт (36-битная шина адреса). Обращение

по адресам, превышающим границу установленной опера-

тивной памяти (или максимально возможного объема),

транслируется на шину PCI, которая имеет 32-битную ад-

ресацию. В компьютерах с 32-разрядной шиной адреса об-

раз BIOS дополнительно проецируется в адреса FFFEOOOOh-

FFFFFFFFh. Иногда используется проекция BIOS в область

FEOOOOh-FFFFFFh, что не позволяет использовать более

11 Зак.№530

16 Мбайт ОЗУ, поскольку система находит только непре-

рывную область расширенной памяти. Для использования

специфических адаптеров ISA, имеющих буфер с адресами

в 16-м мегабайте памяти, в BIOS Setup предусматривают

опцию Memory Hole At 15- 16М. Ее установка не позволяет

использовать оперативную память свыше 16 Мбайт.

Для взаимодействия с интерфейсными адаптерами ISA ин-

тересна верхняя память UMA. Стандартное распределение

верхней памяти выглядит следующим образом:

^ AOOOOh-BFFFFh - Video RAM, 128 Кбайт - видеопамять

(обычно используется не полностью).

^ COOOOh-DFFFFh - Adapter ROM, Adapter RAM,

128 Кбайт - зарезервировано для адаптеров, использую-

щих собственные модули ROM BIOS и/или специаль-

ное ОЗУ, разделяемое с системной шиной.

^ EOOOOh-EFFFFh - свободная область, 64 Кбайт, иногда

занятая под System BIOS.

т FOOOOh-FFFFFh - System BIOS, 64 Кбайт - ROM на

системной плате (в XT используется только FEOOOh-

FFFFFh - 8 Кбайт).

т FDOOOh-FDFFFh - ESCD (Extended System Configuration

Data) - область энергонезависимой памяти, используе-

мая для конфигурирования устройств РпР. Эта область

присутствует только при наличии РпР BIOS; ее положе-

ние и размер жестко не заданы.

В области UMA практически всегда присутствует графичес-

кий адаптер. В зависимости от модели он занимает следую-

щие области:

т MDA RAM - BOOOOh-BOFFFh

т CGA RAM - B8000h-BBFFFh

т EGA ROM - COOOOh-C3FFFh/C7FFFh

m VGA ROM - COOOOh-C7FFFh

m EGA, VGA RAM - AOOOOh-BFFFFh, в зависимости от ви-

деорежима используются следующие области: Graphics -

AOOOOh-AFFFFh; Color Text - B8000h-BFFFFh; Mono

Text - BOOOOh-B7FFFh.

Распространенным потребителем UMA являются расшире-

ния ROM BIOS, расположенные на платах дисковых контрол-

леров, адаптеров SCSI, сетевых картах и т. д. Обычно они

занимают область CSOOOh - CBFFFh/C9FFFh/C8FFFh (для

дисковых контроллеров), но могут перемещаться при кон-

фигурировании адаптеров.

А.2. Пространство ввода/вывода

Процессоры х86 имеют раздельную адресацию памяти и пор-

тов ввода/вывода. Инструкции ввода/вывода порождают

шинные циклы обмена, в которых вырабатываются сигналы

IORD# (чтение порта) и IOWR# (запись в порт) на шинах

ввода/вывода. Эти сигналы отличают пространство ввода/

вывода от пространства памяти, где соответствующие опе-

рации чтения и записи вырабатывают сигналы MEMRD# и

MEMWR#. Для обращения к пространству ввода/вывода пред-

назначены четыре основные инструкции процессора: IN (ввод

в регистр), OUT (вывод из регистра), INS (ввод из порта в

элемент строки памяти) и OUTS (вывод элемента из строки

памяти). Последние две инструкции с префиксом повтора

REP используются для быстрой пересылки блоков данных

между портом и памятью. Разрядность слова, передаваемо-

го за одну инструкцию ввода/вывода, может составлять 8, 16

или 32 бита. В зависимости от выравнивания адреса по гра-

нице слова и разрядности шины это слово может переда-

ваться за один или несколько циклов шины.

Сигналы IORD# и IOWR# вырабатываются и в циклах DMA;

в этом случае на шину адреса подается адрес памяти, к кото-

рой производится доступ, а не порта. Для блокировки сраба-

тьшания дешифратора адреса порта в цикле DMA в шине ISA

имеется сигнал AEN. Селективное программное управление

сигналом AENx для каждого слота шины EISA дает возмож-

ность изолировать пространства ввода/вывода портов, что

используется для программного конфигурирования адресов

адаптеров. В шине ISA разделение слотов не предусмотрено,

что объясняет сложность реализации для нее системы РпР.

Для дешифрации адреса в оригинальном PC из 16 бит ис-

пользовались только младшие 10 (АО-А9), что позволяет об-

ращаться к портам 0-3FFh. Старшие биты адреса, хотя и

поступают на шину, устройствами игнорируются. Так, обра-

щение по адресам 378h, 778h, B78h и F78h воспринимается

устройствами одинаково. В адаптерах для шин МСА и PCI

используются все 16 бит адреса. Современные системные

платы полностью дешифруют адрес.

В реальном режиме процессора программе доступно все про-

странство адресов ввода/вывода. В защищенном режиме (в

частности, в режиме виртуального процессора 86) можно

программно ограничить пространство ввода/вывода, опре-

делив его максимальный размер. Внутри разрешенной обла-

сти доступ может быть разрешен или запрещен для каждого

конкретного адреса. Размер области и карта разрешенных

портов (70 Permission Bitmap) задаются ОС в дескрипторе

сегмента состояния задачи (TSS). При обращении по нераз-

решенному адресу вырабатывается исключение процессора,

обработчик которого определяется ОС. Возможно снятие

задачи-нарушителя. Не исключено, что по обращению к пор-

ту ОС выполнит некоторые действия, создав для програм-

мы иллюзию реальной операции ввода/вывода.

Несколько портов вывода могут иметь совпадающие адреса.

Операции записи они будут отрабатывать нормально. Для

операций считывания ситуация другая. Если несколько пор-

тов ввода имеют совпадающий адрес, при считывании они

передают свои данные на шину. Если они находятся на од-

ной физической шине, возникает конфликт. При прочих рав-

ных условиях для каждого бита шины "побеждает" порт,

выводящий логический ноль. Так, если один порт "хочет"

передать байт OFh, а другой - FOh, то процессор считает OOh.

Если порты находятся на разных физических шинах (напри-

мер, один в ISA, а другой - в PCI), конфликта не будет, по-

скольку шины отделены друг от друга буферами данных.

Каждой шине назначается своя область ввода, и дешифра-

тор, расположенный на системной плате, при чтении откры-

вает соответствующие буферы, так что реально считывают-

ся данные только с одной шины. При записи в порты данные

(и сигнал записи) обычно распространяются по всем ши-

нам компьютера. Адреса Oh-OFFh отведены для устройств

системной платы, чтение по этим адресам не распространя-

ется на шины расширения. Для современных плат со встро-

енной периферией и несколькими шинами (ISA, PCI) рас-

пределением адресов управляет BIOS через регистры кон-

фигурирования чипсета.

Приведенные выше рассуждения справедливы и для про-

странства памяти, но, как правило, они актуальны только

для портов ввода/вывода.

Карта распределения адресов ввода/вывода стандартных

устройств приведена в табл. АЛ. Подразумевается 10-битная

дешифрация адреса.

|

AT и PS/2 |

PC/XT |

Назначение |

|

000-OOF |

000-OOF |

Контроллер DMA #1 8237 |

|

010-01F |

|

PS/2 - расширение DMA # 1 |

|

020-021 |

020-021 |

Контроллер прерываний #1 - 8259А |

|

040-05F |

040-043 |

Таймер (PC/XT: 8253, AT: 8254) |

|

060 |

060 |

Диагностический регистр POST (только запись) |

|

|

060-063 |

Системный интерфейс 8255 |

|

060,064 |

|

Контроллер клавиатуры AT 8042 |

|

061 |

|

Источники NMI и управление звуком |

|

070-07F |

|

Память CMOS и маска NMI |

|

080 |

|

Диагностический регистр |

|

080-08F |

080-083 |

Регистры страниц DMA |

|

090-097 |

|

PS/2: микроканал, арбитр и т. д. |

|

|

ОАО |

Маска NMI |

|

OAO-OBF |

|

Контроллер прерываний #2 - 8259А |

|

OCO-ODF |

|

Контроллер DMA #2 8237А-5 |

|

OFO-OFF |

|

Сопроцессор 80287 |

|

100-1 EF |

|

Управление микроканалом PS/2 |

|

170-177 |

|

Контроллер НЖМД #2 (IDE#2) |

|

1FO-1F7 |

|

Контроллер НЖМД #1 (IDE#1) |

|

AT и PS/2 |

PC/XT |

Назначение |

|

200-207 |

200-20F |

Игровой адаптер |

|

|

210-217 |

Блок расширений |

|

238-23F |

|

COM4 |

|

278-27F |

278-27F |

Параллельный порт LPT2 |

|

|

2А2-2АЗ |

Часы MSM48321RS |

|

2CO-2DF |

2CO-2DF |

EGA #2 |

|

2ЕО-2Е7 |

|

COM4 |

|

2E8-2EF |

|

COM4 |

|

2F8-2FF |

2F8-2FF |

COM2 |

|

300-31F |

|

Плата-прототип |

|

|

320-32F |

Жесткий диск XT |

|

338-33F |

|

COM3 |

|

370-377 |

|

Контроллер НГМД #2 |

|

376-377 |

|

Порты команд IDE#2 |

|

378-37F |

378-37F |

Параллельный порт LPT1 |

|

380-38F |

380-38F |

Синхронный адаптер SDLC/BSC #2 |

|

3AO-3AF |

ЗАО-ЗА9 |

Синхронный адаптер BSC #1 |

|

ЗВО-ЗВВ |

ЗВО-ЗВВ |

Монохромный адаптер (MDA) |

|

ЗВ4-ЗС9 |

|

Видеосистема PS/2 |

|

3BC-3BF |

3BC-3BF |

Параллельный порт LPT1 платы MDA |

|

3CO-3CF |

3CO-3CF |

EGA#1 |

|

3CO-3DF |

3CO-3DF |

VGA |

|

3DO-3DF |

3DO-3DF |

CGA/EGA |

|

ЗЕО-ЗЕ7 |

|

COM3 |

|

3E8-3EF |

|

COM3 |

|

3FO-3F7 |

3FO-3F7 |

Контроллер НГМД #1 |

|

3F6-3F7 |

|

Порты команд IDE#1 |

|

3F8-3FF |

3F8-3FF |

СОМ1 |

А.3. Аппаратные прерывания

Аппаратные прерывания обеспечивают реакцию процессора

на события, происходящие асинхронно по отношению к ис-

полняемому программному коду. Процессоры х86 поддер-

живают таблицу, содержащую определения до 256 процедур

обслуживания прерываний. Немаскируемые прерывания NMI

обрабатываются процессором независимо от состояния флага

разрешения прерывания IF. К ним относятся прерывания,

приходящие по линии NMI, а для процессоров, поддержива-

ющих режим системного управления, еще и по линии SMI#.

Сигнал на линию NMI приходит от схем контроля паритета

памяти, от линии 10СНК шины ISA или SERR# шины PCI.

В машинах класса AT сигнал NMI блокируется до входа про-

цессора установкой бита 7 порта 070h в 1, отдельные источ-

ники - битами 2, 3 порта 061h. Идентифицировать источник

NMI позволяют биты 6, 7 регистра 061h.

В XT NMI вызывается и математическим сопроцессором при

возникновении исключения. Запретить NMI позволяет об-

нуление бита 7 порта OAOh; отдельные источники блокиру-

ются битами 4, 5 регистра 061h; биты 6, 7 регистра 062h

идентифицируют источник.

Обработка маскируемых прерываний может запрещаться ин-

струкцией DI и разрешаться - Е1 (или другим способом воз-

действия на флаг процессора /F). Эти прерывания обслужи-

ваются контроллером, программно-совместимым с 8259А. Он

имеет 8 входов запросов прерываний IRQx от внешних ис-

точников. При обработке запроса контроллер передает по

шине данных 8-битный вектор прерывания, соответствующий

номеру запроса. Этот вектор является индексом, по которо-

му ссылка на процедуру обработки прерывания хранится в

таблице прерываний.

В машинах класса AT используются два контроллера пре-

рываний. Ведущий (первичный) контроллер 8259А#1 обслу-

живает запросы О, 1, 3-7. К его входу 2 подключен ведомый

(вторичный) контроллер 8259А#2, который обслуживает за-

просы 8-15. При этом используется вложенность приорите-

тов - запросы 8-15 со своим рядом убывающих приорите-

тон вклиниваются между запросами 1 и 3 ведущего контрол-

лера, приоритеты запросов которого также убывают с рос-

том номера. В XT один контроллер 8259А обслуживал все 8

линий запросов.

На входы контроллеров прерываний поступают запросы от

системных устройств и плат расширения. Эти линии обо-

значаются как IRQx и имеют общепринятое назначение (табл.

А.2). Прерывания в табл. А.2 расположены в порядке убы-

вания их приоритетов. Номера векторов, соответствующих

линиям запросов контроллеров, система приоритетов и дру-

гие параметры могут задаваться программно при инициали-

зации контроллеров.

|

Имя (номер) |

Вектор |

Назначение |

|

NMI |

02h |

Контроль канала, паритет (в XT - сопроцессор) |

|

0 |

08h |

Таймер (канал 0 8253/8254) |

|

1 |

09h |

Клавиатура |

|

IRQ2 |

OAh |

XT - произвольно, |

|

8 |

70h |

CMOS RTC - часы реального времени |

|

IRQ9 |

71h |

Произвольно |

|

IRQ10 |

72h |

Произвольно |

|

IRQ11 |

73h |

Произвольно |

|

IRQ12 |

74h |

PS/2-Mouse или произвольно |

|

13 |

75h |

Математический сопроцессор |

|

IRQ14 |

76h |

HDC - контроллер НЖМД |

|

IRQ15 |

77h |

Произвольно |

|

IRQ3 |

OBh |

COM2, COM4 |

|

IRQ4 |

OCh |

СОМ1, COM3 |

|

IRQ5 |

ODh |

XT - HDC, |

|

IRQ6 |

OEh |

FDC - контроллер НГМД |

|

IRQ7 |

OFh |

LPT1 - принтер |

Назначение номеров прерываний - процесс двухсторонний:

адаптер должен быть сконфигурирован на использование

конкретной линии шины (джамперами или программно), а

ПО, поддерживающее данный адаптер, должно быть проин-

формировано о номере используемого вектора. Поскольку

прерывания являются дефицитным ресурсом, возникает же-

лание разделить эти линии между несколькими устройства-

ми. Тогда обработчик прерывания устройства, определив, что

источник - не его, вызывал бы обработчик другого устрой-

ства, работающего с той же линией. Однако в шине ISA пре-

рывание вырабатывается по положительному перепаду сиг-

нала на линии запроса. Такой способ подачи сигнала имеет

меньшую помехозащищенность, чем срабатывание по отри-

цательному перепаду, и отрезает путь к нормальному разде-

ляемому использованию линий, для которого полностью

пригоден способ подачи сигнала по низкому уровню. По-

скольку традиционный контроллер позволяет задавать чув-

ствительность - уровень (Level) или перепад (Edge) - толь-

ко для всех входов одновременно, разделяемые прерывания

на шине ISA неработоспособны. Тем не менее, некоторые чип-

сеты, реализующие контроллеры прерываний, допускают

индивидуальное управление чувствительностью каждого вхо-

да. Тогда при соответствующих возможностях BIOS Setup и

адаптеров разделяемые прерывания технически реализуемы.

При чувствительности к уровню сигнал запроса аппаратно-

го прерывания IRQx должен удерживаться генерирующей

схемой по крайней мерю до цикла подтверждения прерыва-

ния процессором. В противном случае источник прерыва-

ния не будет правильно идентифицирован. Обычно адапте-

ры строят так, что сигнал запроса сбрасывается при

обращении программы обслуживания прерывания к соот-

ветствующим регистрам адаптера.

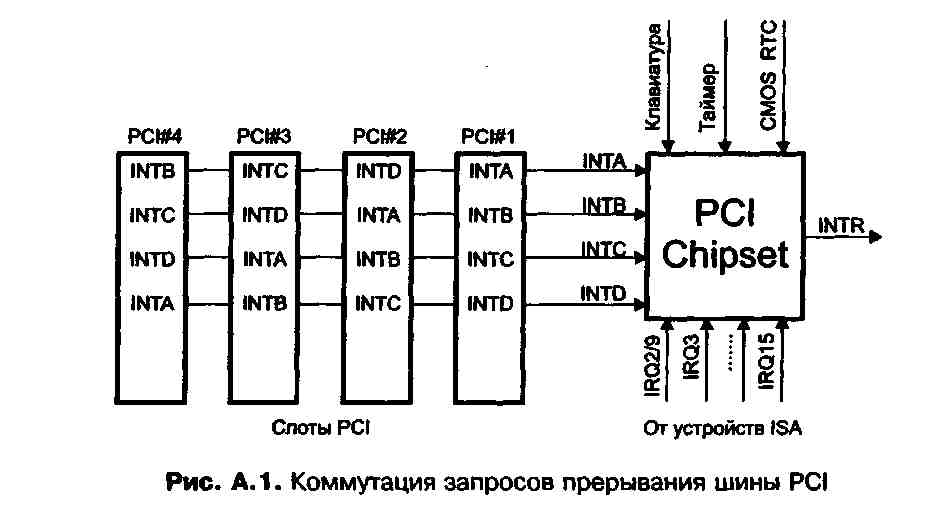

Для запросов прерывания с шины PCI используются 4 ли-

нии, которые обозначают как INTR А, В, С, D. Возможно их

разделяемое использование. Линии циклически сдвигаются в

слотах (рис. А.1) и независимо коммутируются на доступные

IRQx с помощью конфигурационных регистров чипсета.

Линии IRQx, используемые шиной PCI, недоступны для шины

ISA. "Дележку" линий между шинами, а также управление

чувствительностью отдельных линий вьшолняют настройки

BIOS Setup, а также система РпР. В опциях настройки ISA

или Legacy подразумевают использование линий IRQx тради-

ционными адаптерами шины ISA (статическое распределение),

a PCI/PnP - адаптерами шины PCI или адаптерами РпР для

шины ISA (динамическое распределение).

А.4. Прямой доступ к памяти и прямое

управление шиной

Прямой доступ к памяти - DMA (Direct Memory Access) -

метод обмена ПУ с памятью без участия процессора. В обыч-

ном программном обмене (PIO) при пересылке блока дан-

ных, например, из порта в память (инструкция REP INSB),

выполняются следующие действия:

^ Процессор генерирует шинный цикл чтения порта, выстав-

ляя его адрес и формируя сигнал IORD#. Данные из порта

считываются процессором во внутренний шинный буфер.

т Процессор генерирует шинный цикл записи в память,

выставляя адрес ячейки и формируя сигнал MEMWR#.

Данные из внутреннего шинного буфера записываются в

память.

^ Эти шаги автоматически повторяются с изменением ад-

реса памяти. Количество повторов задается в регистре СХ,

инкремент/декремент адреса - флагом DF. Во время пе-

редачи всего блока процессор занят.

В режиме прямого доступа к памяти процессор инициали-

зирует контроллер прямого доступа к памяти - задает на-

чальный адрес, счетчик и режим обмена, после чего осво-

бождается. Обмен производит контроллер и выполняет его

несколько иначе. Контроллер имеет несколько каналов. Для

интерфейса ПУ каждый канал представляется парой сигна-

лов: запрос обмена - DRQx и подтверждение обмена -

DACKx#. В операциях по каналу DMA адрес порта не фигу-

рирует, а используется только пара сигналов, соответствую-

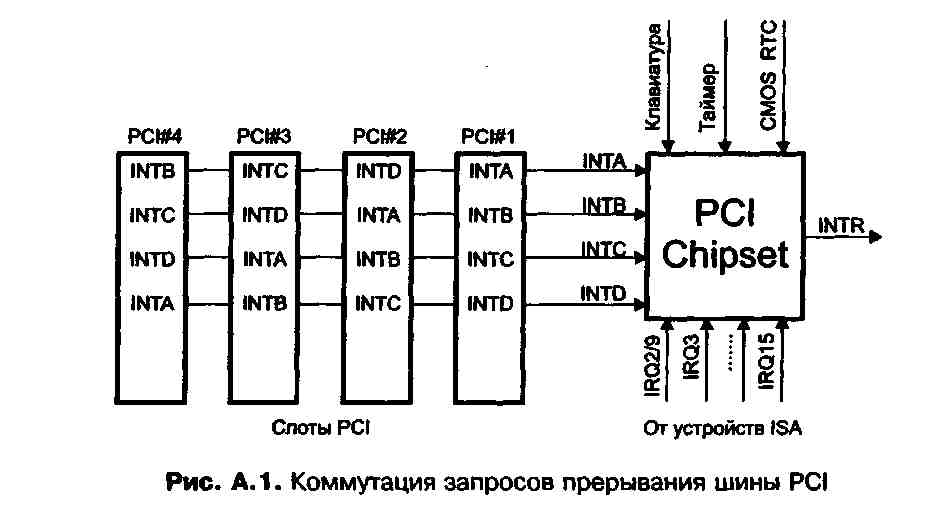

щая номеру канала. Цикл передачи блока в память будет

выглядеть следующим образом (рис. А.2):

1. По сигналу DRQx контроллер запрашивает управление

шиной и дожидается его предоставления процессором

(и другими контроллерами шины).

2. Контроллер выставляет адрес ячейки памяти и форми-

рует в одном цикле шины сигналы IORD#, DACKx# и

MEMWR#. Сигнал DACKx# указывает на то, что операция

выполняется для канала "х", a IORD# - на направление в

канале (для пересьыки из памяти в канал использовался

бы сигнал IOWR#). Чтобы по сигналу IORD# не было лож-

ного чтения (по IOWR# - ложной записи) порта, адрес

которого совпадает с адресом памяти, присутствующим

в цикле DMA, контроллер высоким уровнем сигнала AEN

запрещает портам дешифрацию адреса. Байт, считанный

из канала, в том же цикле шины записывается в ячейку

памяти.

3. Контроллер модифицирует счетчик адреса и повторяет

шаги 1-2 для каждого следующего сигнала DRQx, пока не

будет исчерпан счетчик циклов. В последнем цикле об-

мена контроллер формирует общий сигнал окончания ТС

(Terminate Count), который может быть использован

устройством для формирования сигнала аппаратного пре-

рывания.

Обратная пересылка отличается только тем, что использу-

ются сигналы IOWR# и MEMRD#.

Рис. А.2. Цикл обмена DMA

Процессор при обмене занят только инициализацией кон-

троллера, которая сводится к записи в его регистры несколь-

ких байт. Затем обмен производят системная шина и кон-

троллер. Если выбранный режим обмена не занимает всей

пропускной способности шины, во время операций DMA

процессор может продолжать работу.

Прямой доступ к памяти был использован еще в PC/XT,

где применялась микросхема четырехканального контролле-

ра DMA 18237А. Контроллер имеет 16-разрядные регистры

адреса и счетчики, что позволяет программировать переда-

чу блоков до 64 Кбайт. Для доступа к пространству разме-

ром в 1 Мбайт применили внешние 4-разрядные регистры

страниц DMA, отдельные для каждого канала. В них хра-

нятся биты адреса А[19:16], а битами А[15:0] управляет кон-

троллер. При достижении регистром-счетчиком адреса зна-

чения FFFFh следующее его значение будет OOOOh, а внешний

регистр адреса страницы останется неизменным. Таким об-

разом, если блок начинается не с границы страницы памяти

размером в 64 Кбайт, возможно его "сворачивание в кольцо".

Но если для процессоров 80х86 в реальном режиме "свора-

чиваемые" сегменты могут начинаться с адреса, кратного 10h,

то при прямом доступе границы "сворачиваемого" сегмента

кратны 1 OOOOh. Этот эффект обязательно необходимо учи-

тывать при программировании прямого доступа - блок, пе-

ресекающий границу, должен пересылаться за два сеанса

DMA, между которыми канал (включая регистр страниц)

должен быть повторно инициализирован.

Из четырех каналов DMA XT на шине ISA доступны толь-

ко три (1, 2 и 3). Канал 0 используется для регенерации ди-

намической памяти, адрес регенерируемой строки берется с

линий адреса ISA. Каналы 1, 2 и 3 обеспечивают побайтную

передачу данных и называются 8-битными каналами DMA.

В архитектуре AT подсистему DMA расширили, добавив вто-

рой контроллер 8237А. Его подключили к шине адреса со

смещением на 1 бит. 16-битные регистры адреса способны

управлять линиями адреса А[16:1], младший бит адреса АО

всегда нулевой. Таким образом, второй контроллер передает

данные только по два байта, поэтому его каналы названы

16-битными. За один сеанс второй контроллер способен пе-

редать до 64 К 16-разрядных слов. Регистры страниц для всех

каналов DMA у AT расширены до 8 бит, что делает доступной

для любого канала область памяти размером 16 Мбайт (0-

FFFFFFh). Эффект "сворачивания" сегментов в каналах пря-

мого доступа сохраняется, только для каналов 5, 6 и 7 "коль-

ца" имеют размер 64 К слов и границы, кратные 20000h.

Микросхемы контроллеров 8237А включены каскадно, и ка-

нал 4 недоступен - через него подключается первый контрол-

лер. Стандартное назначение каналов приведено в табл. А.3.

Кроме увеличения числа каналов в AT ввели управление

тиной ISA - Bus-Mastering - со стороны адаптера. Оно опи-

рается на контроллер DMA, выполняющий в данном случае

функции арбитра шины. Для получения управления шиной

адаптер посылает запрос по линии DRQx (только для кана-

лов 5-7) и, получив подтверждение DACKx, устанавливает

сигнал MASTERS. Теперь шиной ISA управляет он, но не

имеет права занимать шину более чем на 15 мкс за сеанс.

В противном случае нарушится регенерация памяти. Интел-

лектуальный контроллер может выполнять более эффектив-

ные процедуры обмена, чем стандартный DMA.

Управление шиной используют высокопроизводительные

адаптеры SCSI и локальных сетей, а также интеллектуаль-

ные графические адаптеры. Однако архитектурой шины до-

ступное им пространство ограничено 16 Мбайт.

Ограничения на доступную память для "чистого" режима

DMA в новых компьютерах снимаются применением расши-

ренных регистров страниц, но об этом должно "знать" ПО.

На шине EISA каналы DMA могут работать в 8-, 16-

и 32-битном режиме и, используя все 32 разряда шины ад-

реса, иметь доступ ко всей памяти компьютера. Каждый ка-

нал программируется на 1 из 4 типов цикла передачи:

^ Compatible - полностью совместим с ISA.

sii Type A - сокращенный на 25% цикл: время одиночного

цикла 875 нс, в блочном режиме время цикла 750 нс. Ра-

ботает почти со всеми ISA-адаптерами с большей скоро-

стью.

^ Type В - сокращенный на 50% цикл (750/500 нс на цикл),

работает с большинством EISA-адаптеров и некоторыми

ISA. Возможен только с памятью, непосредственно до-

ступной контроллеру шины EISA (то есть с памятью на

адаптерах EISA и системной, если EISA является основ-

ной шиной). Если декодированный адрес памяти отно-

сится к 8/16-битной памяти ISA, то контроллер DMA

EISA автоматически переводится в режим Compatible.

т Type С (Burst Timing) - сокращенный на 87,5% цикл,

ориентированный на пакетный режим передачи. Работа-

ет с быстрыми EISA-адаптерами. При обмене 32-битных

устройств с 32-битной памятью позволяет развить ско-

рость обмена до 33 Мбайт/с.

^ В PCI-системах для обмена с устройствами системной пла-

ты (Fast ATA-2 или E-IDE-порты) возможно использова-

ние DMA Type F, при котором между соседними циклами

интервал не должен превышать 3 тактов шины (360 нс).

Для разгрузки системной шины используется 4-байтный

буфер. Режим F может работать только в режиме одиноч-

ной передачи или по запросу и исключительно с инкре-

ментом адреса. На самой шине PCI адаптеры могут ис-

пользовать режим прямого управления шиной, для чего

имеется специальный протокол арбитража.

|

Номер канала DMAft |

о |

1 |

2 |

3 |

4 |

5 |

Q |

7 |

|

|

Стандартное |

XT |

MRFR* |

- |

FDD |

HDD |

Отсутствуют |

|||

|

AT |

- |

SDLC* |

FDD |

HDD* |

Каскад |

- |

- |

- |

|

|

Разрядность, байт |

1 |

2 с четного адреса |

|||||||

|

Максимальный размер блока |

64 Кбайта |

128 Кбайт, четный |

|||||||

|

Граница блока |

Кратна lOOOh |

Кратна 2000h |

|||||||

|

Регистр страниц |

4 бит А16-А19 |

7 бит А17-А23 |

|||||||

|

Адреса регистров:

начального адреса (W)

начального счетчика (W) |

|

|

|

|

|

|

|

|

|

|

087 |

083 |

081 |

082 |

08F |

08В |

089 |

087 |

||

|

000 |

002 |

004 |

006 |

ОСО |

ОСА |

ОС8 |

осе |

||

|

001 |

003 |

005 |

007 |

ОС2 |

ОС6 |

ОСА |

ОСЕ |

||

* SDLC-адаптер устанавливается редко.

HDD-контроллер в AT DMA обычно не использует.

Канал 0 в XT используется для регенерации памяти (MRFR).

Канал 4 доступен только в PS/2 МСА.

А.5. Обмен данными

Открытая архитектура PC предрасполагает использование

различных адаптеров расширения. Чаще всего ПО общается

с адаптерами через порты ввода/вывода, используя преры-

вания, прямой доступ к памяти и непосредственное управ-

ление шиной. Связь через область памяти, к которой при-

писан адаптер, для "нештатных" адаптеров применяется

редко. Выбор способа связи определяется пропускной спо-

собностью, временем отклика на события, происходящие в

адаптере, и допустимой загрузкой процессора.

Программно-управляемый обмен подразумевает следующие

действия:

^ операцию чтения регистра состояния устройства для ана-

лиза его готовности;

^ ожидание готовности (зацикливание предыдущего шага);

^ обмен байтом или словом данных.

Такой обмен сильно загружает процессор, особенно если про-

грамма формирует управляющие сигналы обмена. Так, напри-

мер, работает драйвер параллельного порта в стандартном ре-

жиме, когда строб данных формируется двумя инструкциями

OUT. В результате пропускная способность такого порта в за-

висимости от процессора может быть порядка 150 Кбайт/с.

Если разгрузить процессор от анализа готовности и форми-

рования строба, как, например, в ЕРР-режиме параллельного

порта, то производительность порта можно повысить на по-

рядок. Такой режим обмена программно-управляемым назы-

вать некорректно - это режим программного ввода/вывода с

аппаратным контролем потока, где темп обмена определяет

подключенное устройство. Высокоскоростные режимы PIO

применяются в интерфейсе IDE. Они используют инструк-

ции блочной пересылки REP INS/OUTS, при которых процес-

сор пересылает данные между портом и областью памяти за

минимальное количество тактов системной шины. Посколь-

ку такую скорость ПУ обычно не воспринимают, контроллер

интерфейса "притормаживает" обмен до разумных скоростей,

определяемых режимом обмена. Параметры этих режимов,

называемых PIO Mode, приведены в табл. 6.10.

Обмен по прямому доступу к памяти (как и режим прямого

управления шиной) в наименьшей степени загружает процес-

сор - он занимается лишь анализом состояния и инициали-

зацией канала DMA, но не передачей данных. Время откли-

ка на запрос, когда контроллер "заряжен" на обмен, не

превышает сотен наносекунд. Однако скорость стандартно-

го канала DMA ограничена значением 2/4 Мбайт/с в зави-

симости от разрядности канала. Производительность в ре-

жимах прямого управления шиной обычно выше, чем у

стандартных каналов DMA. Прогрессивные режимы DMA

обеспечивают более высокие скорости обмена: Ultra DMA -

до 33 Мбайт/с.

Обсудим теперь инициализацию и синхронизацию. Инициа-

тором обмена выступает или ПО, или ПУ. Программа ожи-

дает какого-либо события в ПУ, периодически читая его ре-

гистр состояния. Такой способ называется обменом по опросу

готовности. Время реакции может составлять доли мик-

росекунды, когда программа опрашивает устройство моно-

польно. Однако при этом процессор загружен бесполезной

работой. Другой подход - использование аппаратных пре-

рываний, вырабатываемых устройством по событиям, тре-

бующим внимания программы. Программные обработчики

аппаратных прерываний инициализируют блочный обмен

или выполняют одиночную операцию пересылки. Время ре-

акции зависит от множества факторов, включая режим ра-

боты процессора. В защищенном режиме прерывание при-

водит к автоматическому сохранению контекста задачи в

стеке и переключению задач. Эти действия связаны с ин-

тенсивным обменом с памятью, так что отклик может до-

стигать десятков микросекунд или гораздо больше, если за-

действована виртуальная память. В реальном режиме

процессора ответ на прерывание приходит за единицы мик-

росекунд.

Возможно комплексное решение - опрос готовности уст-

ройств по периодическим прерываниям, например, от сис-

темного таймера - polling. Готовое устройство обслуживает-

ся, неготовое - пропускается до следующего прерывания.

Процессор не выполняет бесполезных циклов опроса, а за-

нимается другими задачами. Правда, расходы на обслужи-

вание прерываний остаются, а максимальное время реакции

на событие не может быть меньшим, чем период таймера.

Так работает утилита фоновой печати PRINT.

Активное использование прерываний характерно для мно-

гозадачных ОС.

А.6. Распределение системных ресурсов

Спецификация ISA требует, чтобы всем картам назначались

свои системные ресурсы - области адресов в пространствах

памяти и ввода/вывода, линии запросов прерываний и ка-

налы прямого доступа к памяти. Платы не должны кон-

фликтовать по ресурсам. Задача конфигурирования ослож-

няется из-за отсутствия общего механизма автоматической

передачи установленных параметров прикладному и систем-

ному ПО. Конфигурирование адаптеров выполняется пере-

ключением джамперов, затем установленные параметры за-

носятся в конфигурационные файлы.

Применение энергонезависимой памяти (NVRAM или ее

разновидности - EEPROM), хранящей настройки, облегча-

ет конфигурирование. С соответствующими адаптерами по-

ставляется утилита настройки. Отсюда их названия: Software

Configured (программно конфигурируемые) или Jumperless

(без джамперов). Утилита может проверить выбираемые

установки на отсутствие конфликта, однако достоверность

обнаружения конфликта относительна. Некоторые программ-

но конфигурируемые адаптеры все же имеют джамперы, что

бывает полезно для установки типовой настройки, устраня-

ющей конфликты (например, наложение областей памяти се-

тевого адаптера и видеопамяти). Преимуществом NVRAM

является также отсутствие необходимости в конфигураци-

онных файлах.

Ключевым моментом в автоконфигурировании является изо-

ляция карты от остальных. Тогда ПО конфигурирования

сможет вести с картой диалог, на который не влияет при-

сутствие других устройств. Изоляция карт при конфигури-

ровании заложена в шины МСА, PCI и EISA. В EISA для

каждого слота возможно программное селективное управле-

ние сигналом AEN, запрещающим дешифрацию адресов пор-

тов ввода/вывода. В системе с шиной EISA имеется энерго-

независимая память конфигурирования слотов. Необходи-

мо также обеспечить единый метод двухстороннего обмена

конфигурационной информацией между картой и ПО.

В шину PCI автоматическое конфигурирование установлен-

ных адаптеров заложено изначально. Здесь конфигурирова-

нию также подлежат мосты шины (PCI Bridge) - аппарат-

ные средства подключения PCI к другим шинам. Host

Bridge - главный мост - используется для подключения к

системной шине. Peer-to-Peer Bridge - одноранговый мост -

используется для соединения двух шин PCI (дополнитель-

ные шины PCI позволяют увеличить количество подключа-

емых устройств). При конфигурировании мостов указыва-

ется распределение системных ресурсов по шинам, которые

они связывают. Таким образом, задаются пути транслирова-

ния управляющих сигналов по шинам и управление буфе-

рами данных, обеспечивая для каждого адреса памяти или

ввода/вывода единственную шину назначения, по крайней

мере для операций чтения (операции записи могут быть

широковещательными). Подобная "маршрутизация" необ-

ходима и для сигналов запросов прерываний (каналы DMA

к шине PCI отношения не имеют).

Среди устройств РпР (для шин ISA и PCI) выделяется класс

динамически конфигурируемых устройств DCD (Dynamically

Configurable Device). Ресурсы, используемые ими, динами-

чески переназначаются, не требуя перезагрузки ОС. Если

устройство DCD находится в заблокированном состоянии

(Locked DCD), его ресурсы не могут быть изменены.

Полная поддержка РпР предусматривает наличие РпР BIOS,

плат расширения РпР и/или модулей на системной плате.

Для хранения информации о системных ресурсах необходи-

мо было стандартизовать способы представления конфигу-

рации. В декабре 1994 года компании Compaq, Intel и Phoenix

опубликовали версию 1.03 документа "Extended System

Configuration Data Specification" ("Спецификация расширен-

ных данных о системной конфигурации"), определяющего

методы взаимодействия и структуры данных памяти для

конфигурации устройств ESCD. Данные ESCD хранятся в

энергонезависимом хранилище информации NVS (Non-

volatile Storage). Это может быть память NVRAM или файл

данных для ISA-систем, не имеющих поддержки РпР.

NVRAM может отображаться на область (верхней) памяти,

как полностью, так и постранично. Способ доступа к ESCD

определяется вызовом специальной функции РпР BIOS.

ESCD разрабатывалась на основе форматов описания уст-

ройств шины EISA, в которой имеется специальная энерго-

независимая память и утилиты конфигурирования ECU

(EISA Configuration Utility). Все устройства описываются

через слоты - специальные структуры данных. В стандарте

EISA слот 0 используется для описаний устройств ISA, раз-

мещенных на системной плате. Слоты 1-15 соответствуют

физическим слотам расширения шины EISA, слоты 16-64

определены для виртуальных (не связанных с конкретным

физическим слотом шины) устройств. В ESCD сохранено

примерно то же назначение слотов. Так устройства шины

PCI (включая мосты) описываются слотами 16-64.

С данными ESCD взаимодействует РпР BIOS, а также ОС,

поддерживающая РпР. ACFG BIOS (Auto-Configuration BIOS)

имеет поддержку РпР, в частности автоконфигурирование.

Конфигурированием устройств DCD, которые не были скон-

фигурированы ACFG BIOS во время POST, занимается ме-

неджер конфигурирования, являющийся частью системного

ПО. Каждая РпР-плата сообщает менеджеру конфигуриро-

вания о потребностях и возможных диапазонах настройки

ресурсов. Для обычных (Legacy) плат ISA информация в

ESCD заносится с помощью диалоговой утилиты конфигу-

рирования ICU (ISA Configuration Utility). Таким образом,

конфигурирование плат РпР выполняется автоматически, а

обычных карт - джамперами или утилитами.

А.7. Спецификация РпР для шины ISA

Для изоляции карт ISA, программного распределения сис-

темных ресурсов, конфигурирования и передачи параметров

ОС и прикладному ПО компаниями Intel и Microsoft была

выработана спецификация "Plug and Play ISA Specification";

версия l.Oa была опубликована в мае 1994 года. Рассмотрим

реализацию РпР с точки зрения аппаратных средств.

Конфигурирование в системе РпР состоит из следующих

шагов:

^ Производится изоляция одной карты от всех остальных.

^ Карте назначается CSN (Card Select Number).

^ С карты считываются данные о сконфигурированных и

поддерживаемых ресурсах.

Эти шаги повторяются для всех карт, после чего:

^ производится распределение системных ресурсов, выде-

ляемых каждой карте;

^ каждая карта конфигурируется согласно выбранному рас-

пределению ресурсов и переводится в рабочий режим.

Все шага конфигурирования выполняет POST, если BIOS име-

ет поддержку РпР, или ОС при загрузке. РпР BIOS может

ограничиться конфигурированием и активацией устройств,

участвующих в загрузке. BIOS без поддержки РпР может ис-

пользовать необходимые для загрузки устройства, сконфигу-

рированные с параметрами по умолчанию, а всем остальным

занимается ОС. Конфигурирование выполняется в специаль-

ном состоянии плат, в которое их можно программно переве-

сти специальным ключом инициализации, защищающим кон-

фигурационную информацию от случайного разрушения.

Для конфигурирования карт РпР необходимы три 8-битных

системных порта (табл. А.4), с которыми процессор обща-

ется по инструкциям ввода/вывода с однобайтной передачей

данных. Карты РпР должны использовать 12-битное декоди-

рование адреса ввода/вывода, а не 10-битное, как в тради-

ционных картах ISA.

Порт ADDRESS используется для адресации регистров РпР,

запись в него производится перед обращением к портам

WRITE_DATA и READ_DATA. Он же применяется для записи

последовательности кодов ключа инициализации. Выбор ад-

реса для него обусловлен тем, что "разумные" карты рас-

ширения не будут использовать для записи адрес регистра

состояния стандартного LPT-порта.

Порты WRITEJDATA и READ_DATA используются для обмена

данными с регистрами РпР. Адрес порта WRITEJDATA тради-

ционными картами с 10-битным декодированием будет вос-

приниматься как адрес предыдущего порта, так что конф-

ликт исключен. Перемещаемому адресу порта READJDATA ПО

РпР во время протокола изоляции может легко найти бес-

конфликтное положение. Адрес этого порта сообщается всем

картам записью в их управляющий регистр РпР.

|

Имя порта |

Адрес |

Тип доступа |

|

ADDRESS |

0279h (Printer status port) |

Только запись |

|

WFIITEDATA |

OA79h (Printer status port + 0800h) |

Только запись |

|

READDATA |

Перемещаемый в диапазоне 0203h- |

Только чтение |

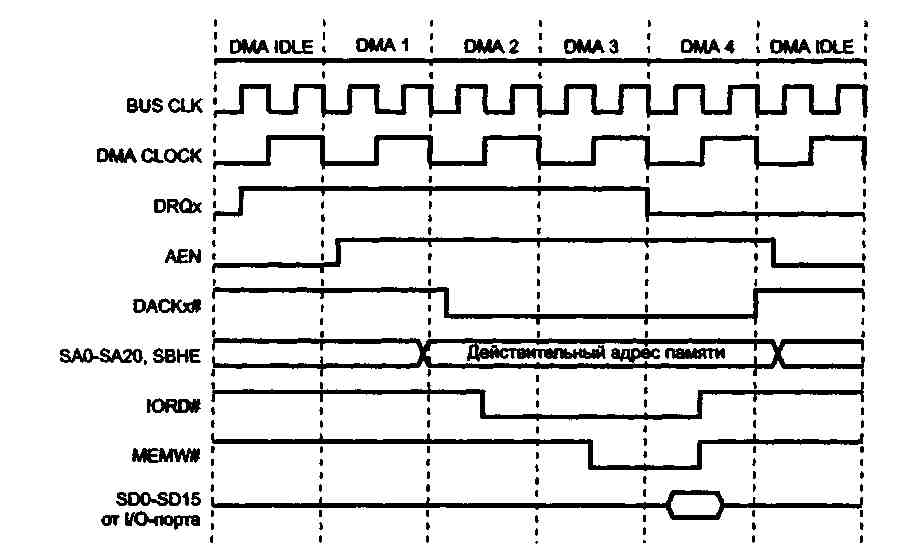

В конфигурационный режим логика РпР переводится клю-

чом инициализации {Initiation key). Ключ представляет со-

бой предопределенную последовательность записей в порт

ADDRESS. Аппаратная логика карты, проверяющая ключ,

основана на сдвиговом регистре с обратными связями LFSR

(Linear Feedback Shift Register), схема которого приведена на

рис. А.3. Во время проверки ключа на вход С1 подается уро-

вень логического 0, а на вход С2 - стробы записи в порт

ADDRESS. Логика, не показанная на рис. А.3, сравнивает код

в сдвиговом регистре с текущей записью и при несовпаде-

нии сбрасывает LFSR в исходное состояние (код 6Ah). В это

же состояние регистр переводится двумя последовательны-

ми записями нулей в порт ADDRESS. Сдвиг в регистре про-

исходит при каждой записи в порт ADDRESS. Если ключ

(последовательность из 32 записей требуемых байт) будет

приложен верно, после последней записи логика карты пе-

рейдет в режим конфигурирования и подготовится к отра-

ботке протокола изоляции. Точная последовательность байт

ключа в hex-формате выглядит следующим образом:

6А. В5. DA, ED. F6. FB. 7D. BE. DF. 6F. 37. IB. OD. 86, СЗ. 61.

ВО. 58. 2С, 16. 8В. 45. А2. Dl. E8. 74, ЗА. 9D. СЕ. Е7. 73. 39.

Рис. А.3. Сдвиговый регистр LFSR карты РпР

Протокол изоляции основан на идентификаторе Serial

Identifier, хранящемся в памяти каждой карты РпР. Этот

идентификатор представляет собой ненулевое 72-битное чис-

ло, состоящее из двух 32-битных полей и 8-битного конт-

рольного кода, вычисляемого с помощью регистра LFSR.

Первое 32-битное поле представляет собой идентификатор

производителя. Второе поле назначается производителем

каждому экземпляру. Здесь может присутствовать серийный

номер; для адаптера Ethernet это может быть частью МАС-

адреса. Принцип построения идентификатора гарантирует,

что в одной системе не могут встретиться две карты с сов-

падающими идентификаторами. Доступ к идентификатору

осуществляется последовательно, начиная с бита 0 нулевого

байта идентификатора производителя и заканчивая битом 7

контрольной суммы. Во время передачи идентификатора на

вход С1 схемы LFSR поступают текущие биты идентифика-

тора, а на вход С2 - стробы чтения регистра SerialJsolation.

В тактах передачи контрольной суммы ее биты берутся с

выхода сдвигового регистра.

Протокол изоляции программно инициируется в любой мо-

мент времени посылкой ключа инициализации, переводящего

все карты в конфигурационный режим. В этом режиме каж-

дая карта ожидает 72 пары операций чтения порта

READ_DATA. Ответ каждой карты на эти операции опреде-

ляется значением очередного бита ее идентификатора.

Если текущий бит идентификатора карты имеет единичное

значение, ее буфер шины данных в первом чтении пары вы-

водит на шину значение 55h. Если текущий бит нулевой, то

буфер работает на чтение шины и логика карты анализиру-

ет ответ других карт - проверяет наличие комбинации 01 в

битах D[1:0] (младшие биты 55h). В следующем цикле чте-

ния пары карта с единичным битом выводит число AAh, a

карта с нулевым текущим битом проверяет наличие комби-

нации 10 в битах D[1:0] (младшие биты AAh). Если карта,

просматривающая вывод данных другими картами, обнару-

жила корректные коды в обоих циклах чтения пары, она в

данной итерации изоляции исключается. Если карта в теку-

щей паре управляла шиной или читала шину, но не обнару-

жила корректных активных ответов других карт, она сдви-

гает идентификатор на один бит и готовится к приему

следующей пары циклов чтения. Эта последовательность

выполняется для всех 72 бит идентификатора. В конце про-

цесса останется лишь одна карта. Записью в управляющий

регистр ей назначается номер CSN, по которому она будет

использоваться в дальнейших операциях. Карта с назначен-

ным CSN в следующих итерациях протокола изоляции не

участвует (на пары чтений не отвечает).

Во время протокола изоляции карты не имеют права удли-

нять шинные циклы с помощью сигнала IOCHRDY, посколь-

ку это привело бы к неопределенности результатов наблю-

дения за "соседями".

Программа конфигурирования проверяет данные, возвращае-

мые во время пар циклов чтения, и побитно собирает про-

читанный идентификатор. Если в паре приняты байты 55h

и AAh, соответствующий бит считается единичным, в дру-

гих случаях - нулевым. При приеме идентификатора про-

грамма подсчитывает контрольную сумму и сравнивает ее с

принятой. Несовпадение или отсутствие среди принятых

байт 55h и AAh указывает на то, что выбранный адрес пор-

та READ_DATA конфликтует с каким-либо устройством. Тог-

да программа производит итерацию, переместив адрес пор-

та READ_DATA в допустимом диапазоне адресов. Если при

переборе адресов не удается считать корректного идентифи-

катора, принимается решение об отсутствии карт РпР в си-

стеме (вообще или с неназначенными CSN).

Программа должна обеспечить задержку 1 мс после подачи

ключа перед первой парой чтений и 250 мкс между парами

чтений. Это дает карте время для доступа к информации,

которая может храниться в медленных устройствах энерго-

независимой памяти.

По завершении протокола изоляции ПО имеет список иден-

тификаторов обнаруженных карт и присвоенных им номеров,

сообщенных картам. Далее общение ПО с картой идет по ее

номеру CSN, фигурирующему в командах РпР. Нулевой CSN

присваивается картам по программному или аппаратному

сбросу и используется как широковещательный адрес.

Обращения к регистрам РпР представляют собой операции

записи/чтения портов ввода/вывода по адресам WRITE_DATA/

READ_DATA соответственно. При этом для указания конк-

ретного регистра РпР используется индекс - номер регист-

ра, предварительно записанный в регистр ADDRESS.

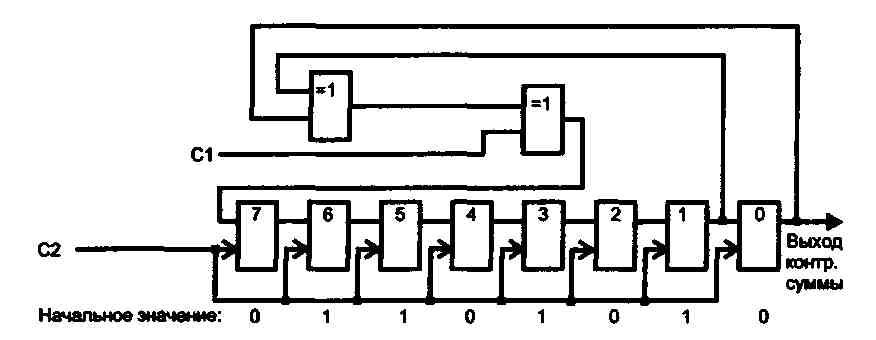

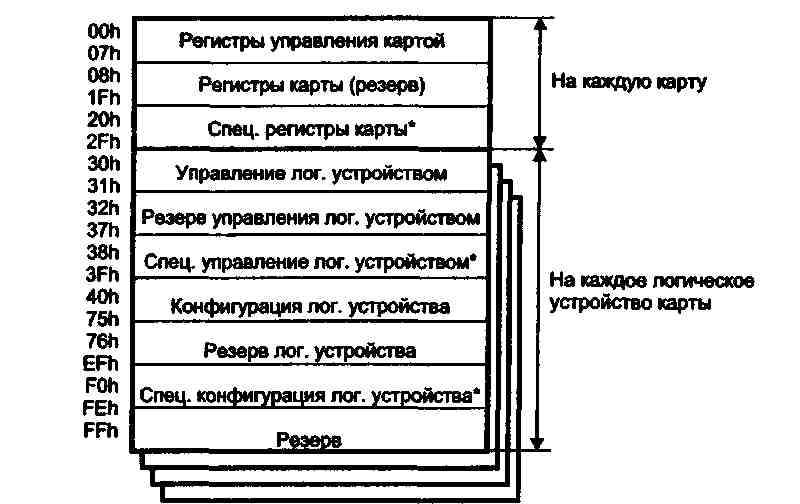

Каждая карта имеет стандартный набор регистров РпР; часть

из них относится к карте в целом, а часть - к логическим

устройствам (ЛУ), входящим в карту. В любой момент вре-

мени в индексном пространстве регистров РпР отобража-

ются общие регистры карты и регистры только одного ЛУ

(рис. А.4). Выбор ЛУ, с которым производится общение, осу-

ществляется записью в регистр Logical Device Number.

Рис. А.4. Конфигурационные регистры РпР (* - определяется

разработчиком)

С точки зрения системы РпР карта пребывает в некотором

состоянии. Состояние Isolate используется в протоколе изо-

ляции, описанном выше.

Программирование карты начинается с команды

WAKE[CSN] - записи байта CSN в регистр с индексом 3. Эта

операция переводит карту с указанным CSN в состояние

Config (конфигурирование), а остальные карты переходят в

состояние Sleep. Для карты выполняются операции чтения

ее конфигурационной информации (как карты в целом, так

и Л У) и программирования используемых ресурсов. Про-

граммирование каждого ЛУ завершается установкой его бита

активации, после чего оно активизируется на шине ISA. Про-

граммирование всей карты завершается переводом ее в со-

стояние Wait/or key (ожидание ключа). По окончании кон-

фигурирования все карты РпР должны быть переведены в

это состояние - тогда их случайное реконфигурирование

будет блокировано 32-байтным ключом.

Доступ к регистрам РпР через ключ возможен в любое вре-

мя. Возможно переназначение CSN "на ходу" - это требует-

ся в устройствах, допускающих динамическое включение/

выключение, док-станциях (Docking Stations) и при управ-

лении энергопотреблением.

Все ЛУ карт РпР должны обеспечивать следующую мини-

мальную функциональность:

^ Регистры ресурсов при чтении должны отражать факти-

ческие текущие настройки.

^ Бит активации при чтении должен отражать правдивое

состояние активности устройства на шине ISA.

ш Если программа пытается "навязать" карте неподдержи-

ваемую конфигурацию, устройство не должно активиро-

ваться; соответственно, при чтении его флаг активации

должен быть сброшен.

Стандартные регистры управления картой (табл. А.5) исполь-

зуются для адресации карты и ее ЛУ, а также для чтения кон-

фигурационной информации (дескрипторов). Дескрипторы

ресурсов могут быть считаны побайтно из регистра Resource

Data. При этом могут использоваться данные в короткой или

длинной форме. Короткая форма (Small Resource Data Type)

допускает дескрипторы до 7 байт, длинная форма (Large

Resource Data Type) - до 64 Кбайт. Форма дескриптора и имя

описываемого ресурса определяются первым байтом дескрип-

тора. Его последующие байты описывают требуемые ресурсы

и возможные варианты (диапазоны) конфигурирования.

|

Регистр |

Индекс и тип |

Назначение |

|

SetRD DATA |

OOh.WO |

Установка адреса порта для чтения. |

|

Serial Isolation |

01 h, RO |

Чтение этого регистра в состоянии |

|

Config Control |

02h,WO |

Бит [2]- сброс CSN в 0 |

|

Wake[CSNJ |

03h,WO |

Запись в этот регистр приведет карту |

|

Resource Data |

04h,RO |

Чтение этого регистра возвращает |

|

Status |

05h, RO |

Регистр состояния. Единичное |

|

Регистр |

Индекс и тип |

Назначение |

|

Card Select |

06h,RW |

Регистр хранения селективного адре- |

|

Logical Device |

07h, RW |

Выбор текущего ЛУ, к которому отно- |

|

Card Level |

08h-lFh |

Зарезервированы |

|

Card Level, |

20h-2Fh |

Используются по усмотрению произ- |

|

Регистр |

Индекс и тип |

Назначение |

|

Activate |

30h,RW |

Регистр активации: |

|

I/O Range |

31 h, RW |

Регистр проверки диапазона адресов |

|

Logical Device |

32h-37h |

Зарезервированы |

|

Logical Device |

38h-3Fh |

Используются по усмотрению произ- |

Стандартные регистры управления ЛУ (табл. А.6) исполь-

зуются для активации карт и проверки отсутствия конф-

ликтов на шине ISA в выбранном диапазоне адресов ввода/

вывода. Когда включен режим проверки конфликтов, на чте-

ние по любому адресу установленного диапазона портов вво-

да/вывода ЛУ отвечает байтом 55h или AAh в зависимости

от состояния бита 0 регистра проверки диапазона адресов.

В рабочем режиме этот "автоответчик" отключен.

Оперативные данные конфигурирования доступны через

регистры ЛУ. Каждое логическое устройство имеет собствен-

ные дескрипторы используемых системных ресурсов:

^ Обычные 24-битные (4) и 32-битные (4) дескрипторы

памяти. Поля базового адреса и длины неиспользуемого

дескриптора памяти должны быть нулевыми. Одна кар-

та не может одновременно использовать 24-битные и

32-битные дескрипторы памяти.

^ Дескрипторы областей портов ввода/вывода (8). Поле

базового адреса неиспользуемого дескриптора портов вво-

да/вывода должно быть нулевым. Размер области адре-

сов определяется в блоке данных описателя.

^ Дескрипторы запросов прерываний (2). Неиспользуемый

селектор запроса прерывания должен быть нулевым (ну-

левой номер запроса занят системным таймером). Для

линии IRQ2/9 шины ISA применяют номер 2.

^ Дескрипторы каналов прямого доступа к памяти. Неис-

пользуемый дескриптор канала должен иметь значение 4

(этот канал недоступен - используется для каскадирова-

ния контроллеров).

Назначение регистров дескрипторов и их положение в ин-

дексном пространстве РпР описано в табл. А.7.

|

Индекс и тип |

Назначение |

|

40h-5Fh - Обычные дескрипторы памяти |

|

|

40h, RW |

Дескриптор памяти ft базовый адрес памяти, |

|

Индекс и тип |

Назначение |

|

41h, RW |

Дескриптор памяти 0: базовый адрес памяти, |

|

42h, RW |

Дескриптор памяти О: управление. |

|

43h, RW |

Дескриптор памяти 0: размер или старший адрес |

|

44h, RW |

Дескриптор памяти 0: размер или старший адрес |

|

45h-47h |

Заполнитель (зарезервировано) |

|

48h-4Ch |

Дескриптор памяти 1 (аналогично предыдущему) |

|

4Dh-4Fh |

Заполнитель (зарезервировано) |

|

50h-54h |

Дескриптор памяти 2 (аналогично предыдущему) |

|

55h-57h |

Заполнитель (зарезервировано) |

|

58h-5Ch |

Дескриптор памяти 3 (аналогично предыдущему) |

|

5Dh-5Fh |

Заполнитель (зарезервировано) |

|

60h-6Fh -Дескрипторы пространства ввода/вывода |

|

|

60h, RW |

Дескриптор портов 0: базовый адрес, биты [15:8]. |

|

61 h, RW |

Дескриптор портов 0: базовый адрес, биты [7:0] |

|

62h-63h, RW |

Дескриптор портов 1 - аналогично |

|

64h-65h, RW |

Дескриптор портов 2 - аналогично |

|

66h-67h, RW |

Дескриптор портов 3 - аналогично |

|

68h-69h, RW |

Дескриптор портов 4 - аналогично |

|

6Ah-6Bh, RW |

Дескриптор портов 5 - аналогично |

|

6Ch-6Dh, RW |

Дескриптор портов 6 - аналогично |

|

6Eh-6Fh, RW |

Дескриптор портов 7 - аналогично |

|

Индекс и тип |

Назначение |

|

70h-73h - Дескрипторы запросов прерываний |

|

|

70h, RW |

Селектор запроса прерывания 0: Биты [3:0] задают |

|

71 h, RW |

Тип сигнала запроса прерывания 0-. |

|

72h,RW |

Селектор запроса прерывания 1 |

|

73h, RW |

Тип сигнала запроса прерывания 1 |

|

74h-75h - Дескрипторы каналов прямого доступа |

|

|

74h, RW |

Селектор 0 канала DMA. Биты [2:0] задают номер |

|

75h, RW |

Селектор 1 канала DMA |

|

76h-A8h - 32-битные дескрипторы памяти |

|

|

76h, RW |

32-битный дескриптор памяти 0: базовый адрес |

|

77h, RW |

32-битный дескриптор памяти 0: базовый адрес |

|

78h, RW |

32-битный дескриптор памяти 0'. базовый адрес |

|

79h, RW |

32-битный дескриптор памяти 0: базовый адрес |

|

7Ah,RW |

32-битный дескриптор памяти 0: управление |

|

Индекс и тип |

Назначение |

|

7Bh, RW |

32-битный дескриптор памяти (h |

|

7Ch, RW |

32-битный дескриптор памяти 0: |

|

7Dh, RW |

32-битный дескриптор памяти 0-. |

|

7Eh, RW |

32-битный дескриптор памяти 0'. |

|

7Fh |

Заполнитель (зарезервировано) |

|

80h-88h |

32-битный дескриптор памяти 1 |

|

89h-8Fh |

Заполнитель (зарезервировано) |

|

90h-98h |

32-битный дескриптор памяти 2 |

|

99h-9Fh |

Заполнитель (зарезервировано) |

|

AOh-A8h |

32-битный дескриптор памяти 3 |