4. Шины расширения

Шины расширения (Expansion Bus) предназначены для под-

ключения различных адаптеров ПУ. Интерфейсы шин рас-

ширения PC ведут историю с 8-битной шины ISA. Ее от-

крытость обеспечила появление широкого спектра плат

расширений, позволивших использовать PC в различных

сферах. С появлением АТ-286 шина была расширена по раз-

рядности и возможностям. Шина EISA была призвана сде-

лать обмен еще более производительным и надежным. Она

содержала прогрессивные идеи автоматизации конфигури-

рования (прототип РпР), позволяя устанавливать и ISA-адап-

теры. Шина МСА, предложенная IBM, не была поддержана

производителями PC, так как ее спецификация была закры-

той. С появлением процессора 486 родилась высокоскорост-

ная локальная шина VLB. Однако она являлась дополнени-

ем к слоту шины ISA/EISA и использовалась в основном

лишь для графических карт и дисковых контроллеров. Прин-

ципиальная привязка к шине процессора 486 не обеспечила

ей долголетия. Современная скоростная шина PCI является

стандартной для компьютеров с процессорами х86 всех по-

колений старше четвертого, она используется в Power PC и

других платформах. Развитием шины PCI, нацеленным на

дальнейшее ускорение обмена, явился порт AGP, предназна-

ченный для подключения графических адаптеров. Для блок-

нотных компьютеров, поначалу имевших закрытую архитек-

туру, потребность в подключении периферии привела к

появлению стандартизованной шины PCMCIA, впоследствии

переименованной в PC Card.

Шины расширения системного уровня позволяют адаптерам

максимально использовать системные ресурсы PC: простран-

ства памяти и ввода/вывода, прерывания, каналы прямого

доступа к памяти. Как следствие, изготовителям модулей

расширения приходится точно следовать протоколам шины,

выдерживая жесткие частотные и нагрузочные параметры, а

также временные диаграммы. Отклонения приводят к не-

совместимости с некоторыми системными платами. Если при

подключении к внешним интерфейсам это приведет к нера-

ботоспособности только самого устройства, то некорректное

подключение к системной шине может блокировать работу

всего компьютера. Следует также учитывать ограниченность

ресурсов PC. Самые дефицитные из них - линии запросов

прерываний (каналы прямого доступа можно заменить на

активное управление шиной PCI). Проблемы распределения

ресурсов на шинах решаются по-разному, но чаще всего при-

меняется технология РпР.

В табл. 4.1 даны характеристики стандартных шин расши-

рения PC.

|

Шина |

Пропускная |

|

Bus- |

ACFG** |

Разрядность |

Разрядность |

Частота, |

|

DMA |

|||||||

|

БД-8 |

4 |

3 |

- |

- |

8 |

20 (1 Мбайт) |

8 |

|

БД-16 |

8Д16) |

8 |

+ |

- |

16 |

24 (16 Мбайт) |

8/(16) |

|

ЕБД |

33,3 |

8 |

+ |

+ |

32 |

32 (4 Гбайт) |

8.33 |

|

МСД-16 |

16 |

- |

+ |

+ |

16 |

24 (16 Мбайт) |

10 |

|

МСД-32 |

20 |

- |

+ |

+ |

32 |

32 (4 Гбайт) |

10 |

|

VLB |

132 |

- |

(+) |

- |

32/64 |

32 (4 Гбайт) |

33-50(66) |

|

pa |

132/264 |

- |

- |

+ |

32/64 |

32 (4 Гбайт) |

33(66) |

|

гсмад |

- |

- |

- |

+ |

16 |

26 (64 Мбайт) |

33 |

* Указана максимальная пропускная способность. Реальная примерно в 2

раза ниже за счет прерываний, регенерации и протокольных процедур.

** Поддержка автоматического конфигурирования. Для ISA PnP являет-

ся позднейшей надстройкой, реализуемой адаптерами и ПО.

Шины расширения конструктивно оформляются в виде ще-

левых разъемов (слотов) на системной плате для установки

плат адаптеров. Унификация системных плат, корпусов и

плат расширения обеспечивается:

^ стандартизацией размеров, количества контактов и элект-

рического интерфейса слотов шин расширения;

^ фиксированным расстоянием от слота до задней кромки

платы;

т фиксированным шагом между соседними слотами, а также

их привязкой к крепежным точкам и разъему клавиатуры;

йй определением максимальных габаритов (длины и высо-

ты) карт расширения;

^ определением геометрии нижнего края платы расшире-

ния, формы и размера фиксирующей скобки.

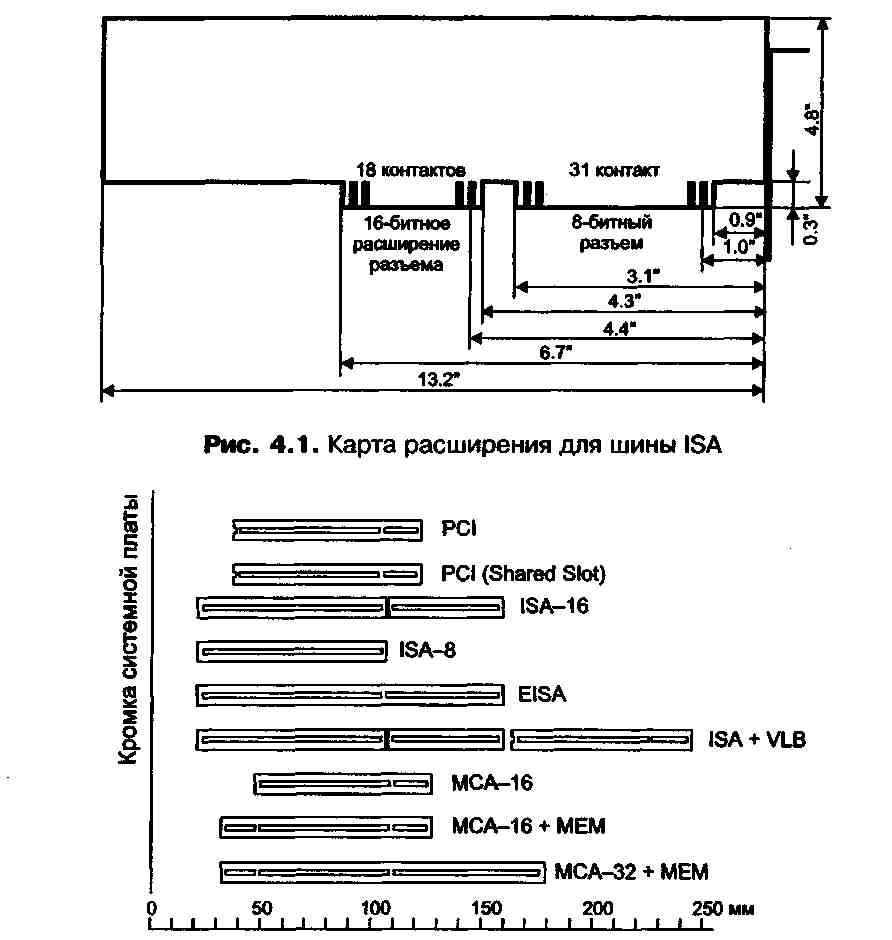

Размеры карт расширения для самой популярной шины -

ISA - приведены на рис. 4.1.

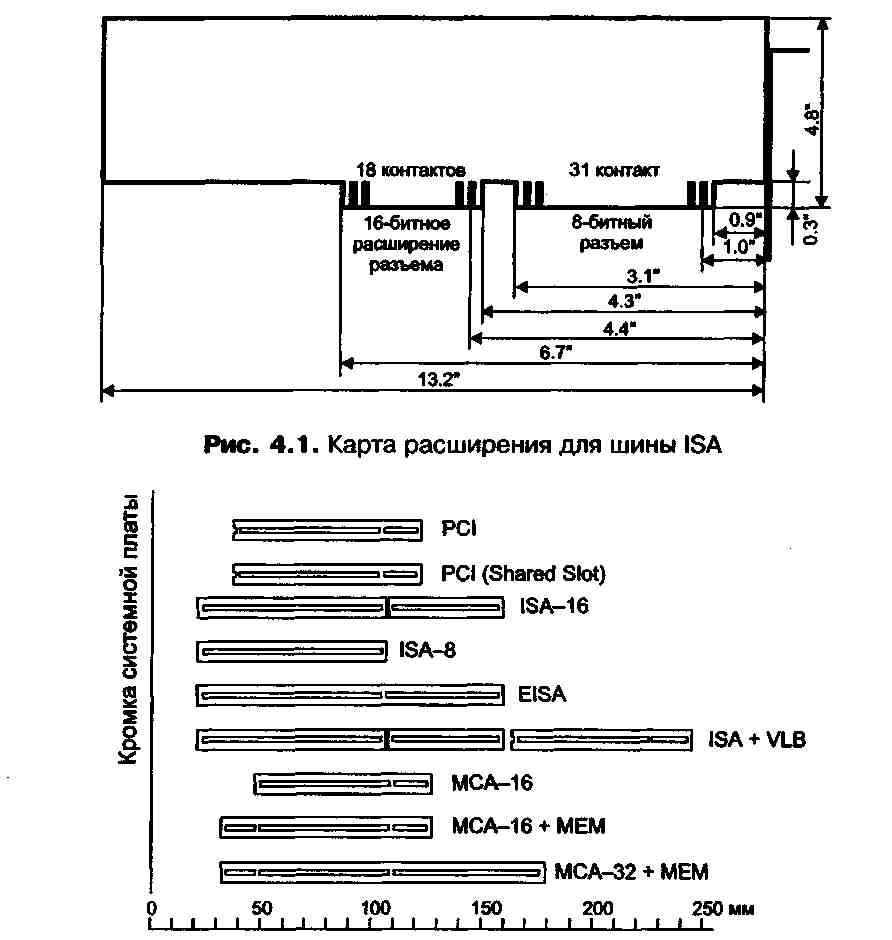

Рис. 4.2. Вид и положение слотов шин расширения

Типы слотов легко определить визуально (рис. 4.2). На этом

рисунке присутствие всех типов шин условно - реально на

системных платах находится не более двух-трех типов сло-

тов. Распространенные сочетания: ISA+PCI, ISA+VLB,

EISA+PCI, EISA+VLB. Фирмой ASUSTek применяется слот

"Media BUS", дополняющий слот PCI сигналами шины ISA.

У адаптеров для шины PCI, в отличие от ISA/EISA и VLB,

компоненты расположены на левой стороне печатной пла-

ты. Для экономии места на системной плате используют так

называемый разделяемый слот (Shared Slot). На самом деле

это разделяемое окно на задней стенке корпуса, которое мо-

жет использоваться либо картой ISA, либо картой PCI. Та-

ким образом, максимальное суммарное количество доступ-

ных слотов оказывается на единицу меньшим, чем видимое

количество.

Для низкопрофильных корпусов системные платы имеют всего

один слот расширения, в который устанавливается специаль-

ная плата-переходник Riser Card. Этот переходник специфи-

чен для модели системной платы (корпуса), поскольку на

его краевой разъем заводятся линии нескольких системных

шин. Если Riser Card имеет слоты только шины ISA, он обыч-

но вставляется в стандартный слот ISA-16. С точки зрения

уменьшения наводок и паразитных емкостей лучше использо-

вать специальные платы с одним разъемом, чтобы не перегру-

жать шину неиспользуемыми проводниками и разъемами.

Шины расширения допускают конфигурирование, которое

предполагает в основном настройку их временных параметров:

^ Для шины VLB применяется перемычка, управляющая де-

лителем частоты сигнала синхронизации в зависимости от

того, превышает ли системная частота 33,3 МГц.

^ Для шины PCI частота синхронизации определяется ча-

стотой системной шины процессора. Кроме того, режи-

мы могут определяться в BIOS Setup.

йа Для шины ISA кроме частоты (которая должна быть по-

рядка 8 МГц) задают время восстановления для 8- и

16-битных обращений к памяти и вводу/выводу. Неус-

тойчивая работа адаптеров может потребовать замедле-

ния шины ISA. Понижение ее производительности не от-

ражается на общей производительности современных

компьютеров.

^ Иногда для шин ISA и PCI опциями BIOS Setup прихо-

дится распределять системные ресурсы (линии запросов

прерываний)(см. приложение А).

4.1. Шины ISA, EISA и PC-104

ISA Bus (Industry Standard Architecture) - шина расшире-

ния, применявшаяся с первых моделей PC и ставшая про-

мышленным стандартом. В компьютере XT использовалась

шина с разрядностью данных 8 бит и адреса - 20 бит. В

компьютерах AT ее расширили до 16 бит данных и 24 бит

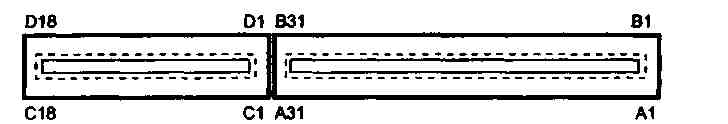

адреса. В таком виде она существует и поныне. Конструк-

тивно шина выполнена в виде двух щелевых разъемов с ша-

гом выводов 2,54 мм (0,1 дюйма) (см. рис. 4.3). Подмноже-

ство ISA-8 использует только 62-контактный слот (ряды А,

В), в ISA-16 применяется дополнительный 36-контактный

слот (ряды С, D).

Шина обеспечивает возможность отображения 8- или 16-бит-

ных регистров на пространство ввода/вывода и памяти.

Диапазон адресов памяти ограничен областью UMA (выше

AOOOOh). Для шины ISA-16 опциями BIOS Setup может быть

разрешено пространство между 15-м и 16-м мегабайтами па-

мяти (при этом компьютер не сможет использовать более

15 Мбайт ОЗУ). Диапазон адресов ввода/вывода сверху огра-

ничен количеством используемьк для дешифрации бит адре-

са, нижняя граница ограничена областью адресов 0-FFh, за-

резервированных под устройства системной платы. В PC была

принята 10-битная адресация ввода/вывода, при которой ли-

нии адреса А[15:10] устройствами игнорировались. Таким об-

разом, диапазон адресов устройств шины ISA ограничивает-

ся областью 100h-3FFh, то есть всего 758 адресов 8-битных

регистров. На некоторые из адресов претендуют системные

устройства (см. табл. А.1). Впоследствии стали применять

12-битную адресацию (диапазон lOOh-FFFh). При ее исполь-

зовании необходимо учитывать возможность присутствия на

шине старых 10-битных адаптеров, которые "отзовутся" на

адрес с подходящими ему битами А[9:0] во всей допустимой

области 12-битного адреса четыре раза (у каждого 10-битно-

го адреса будет еще по три 12-битных псевдонима).

Рис. 4.3. Слот ISA

Шина ISA-8 может предоставить до 6 линий запросов пре-

рываний, ISA-16 - 11. Часть их могут "отобрать" устрой-

ства системной платы или шина PCI.

Шина позволяет использовать до трех 8-битных каналов DMA.

На 16-битной шине доступны еще три 16-битных канала. Сиг-

налы 16-битных каналов могут использоваться для прямого

управления шиной устройством Bus-Master. При этом канал

DMA применяется для арбитража шины, а адаптер Bus-Master

формирует все адресные и управляющие сигналы шины, не

забывая передать управление шиной процессору не позднее,

чем через 15 мкс (чтобы не нарушить регенерацию памяти).

Все перечисленные ресурсы системной шины должны быть

бесконфликтно распределены. Бесконфликтность подразу-

мевает следующее:

^ Каждое устройство должно управлять шиной данных

только при чтении по своим адресам или по используе-

мому им каналу DMA. Области адресов для чтения не

должны пересекаться. "Подсматривать" операции запи-

си, "адресованные не ему", не возбраняется.

ш Назначенную линию IRQx или DRQx устройство должно

держать на низком уровне в пассивном состоянии и пере-

водить в высокий уровень для активации запроса. Неис-

пользуемыми линиями запросов устройство управлять не

имеет права, они должны быть электрически откоммути-

рованы или подключаться к буферу, находящемуся в тре-

тьем состоянии. Одной линией запроса может пользовать-

ся только одно устройство. Такая нелепость (с точки

зрения схемотехники ТТЛ) была допущена в первых PC

и из требований совместимости тиражируется до сих пор.

Задача распределения ресурсов для старых адаптеров реша-

лась с помощью джамперов, затем появились программно

конфигурируемые устройства, которые вытесняются авто-

матически конфигурируемыми платами РпР.

С появлением 32-битных процессоров делались попытки

расширения разрядности шины, но все 32-битные шины ISA

не являются стандартизованными, кроме EISA.

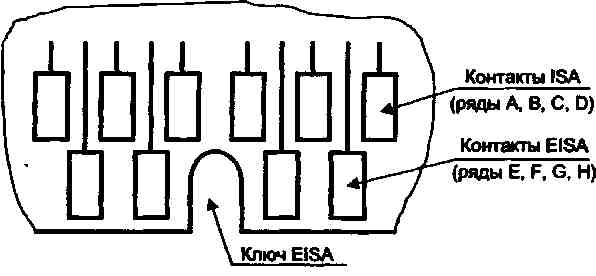

EISA Bus (Extended ISA) - стандартизованное расширение

ISA до 32 бит. Конструктивное исполнение обеспечивает со-

вместимость с ней ISA-адаптеров (рис. 4.4). Узкие дополни-

тельные контакты расширения (ряды Е, F, G, Н) располо-

жены между ламелями (контактными площадками) разъема

ISA и ниже ламелей А, В, С, D таким образом, что адаптер

ISA, не имеющий дополнительных ключевых прорезей в кра-

евом разъеме, не достает до них. Установка карт EISA в сло-

ты ISA недопустима, поскольку ее цепи попадут на контак-

ты ISA, в результате чего системная плата окажется

неработоспособной (к счастью, "без дыма").

Рис. 4.4. Разъем шины EISA

Для режимов EISA используются дополнительные управля-

ющие сигналы, обеспечивающие более эффективные режи-

мы передачи. В обычном (не пакетном) режиме передачи за

каждую пару тактов может быть передано до 32 бит (один

такт на фазу адреса, один - на фазу данных). В пакетном

режиме (Burst Mode) пакеты данных пересылаются без ука-

зания текущего адреса внутри пакета. В пакете очередные

данные передаются в каждом такте шины, длина пакета дос-

тигает 1024 байт. Шина предусматривает более производи-

тельные режимы DMA (см. прил. А4), при которых скорость

обмена может достигать 33 Мбайт/с. Линии запросов пре-

рываний допускают разделяемое использование, причем со-

храняется совместимость с ISA-картами: каждая линия за-

проса может программироваться на чувствительность как по

высокому (как в ISA), так и по низкому уровню. Шина до-

пускает потребление каждой картой расширения мощности

до 45 Вт, но это не означает, что мощность блока питания

для 8 слотов должна быть более 360 Вт - полную мощность

не потребляет ни один из адаптеров.

Многие решения EISA напоминают МСА. Каждый слот (мак-

симум - 8) и системная плата имеют селективное разреше-

ние адресации ввода/вывода и отдельные линии запроса и

подтверждения управления шиной. Арбитраж запросов вы-

полняет устройство ISP (Integrated System Peripheral). При-

оритеты (в порядке убывания): регенерация, DMA, CPU, Bus-

Master. Обязательной принадлежностью системной платы с

шиной EISA является энергонезависимая память конфигу-

рации NVRAM, в которой хранится информация об ус-

тройствах EISA для каждого слота. Формат записей стан-

дартизован, для модификации информации применяется

специальная утилита ECU (EISA Configuration Utility). Ар-

хитектура позволяет при использовании программно кон-

фигурируемых адаптеров автоматически разрешать конфлик-

ты, но в отличие от РпР не допускает динамического

конфигурирования - после выхода из режима конфигури-

рования необходима перезагрузка. Изолированный доступ

к портам ввода/вывода каждой карты во время конфигури-

рования обеспечивается просто: сигнал AEN, разрешающий

декодирование адреса в цикле ввода/вывода, на каждый слот

приходит по отдельной линии AENx, в это время программ-

но-управляемой. Так можно обращаться и к картам ISA, но

из этого нельзя извлечь выгоды, поскольку они не поддер-

живают обмена конфигурационной информацией. Идеи кон-

фигурирования EISA были использованы в спецификации

РпР для шины ISA (формат конфигурационных записей

ESCD напоминает NVRAM EISA).

EISA - дорогая, но оправдывающая себя архитектура, при-

меняющаяся в многозадачных системах и на серверах, где

требуется высокоэффективное расширение шины ввода/вы-

вода. Перед шиной PCI у нее есть преимущество в количе-

стве слотов (8 против 4).

Назначение контактов слотов шин ISA и EISA приведено в

табл. 4.2 и 4.3.

|

РядР |

Ряд В |

N" |

РЯДА |

РЯДЕ |

|

GND |

GND |

1 |

10СНК |

CMD^ |

|

+5 В |

Reset |

2 |

Data 7 |

START" |

|

+5 В |

+5 В |

3 |

Data 6 |

EXRDY |

|

Unused |

IRQ 2/9' |

4 |

Data 5 |

EX32# |

|

Unused |

-5В |

5 |

Data 4 |

GND |

|

Key |

DRQ2 |

6 |

Data3 |

Key |

|

Unused |

-12В |

7 |

Data 2 |

EX16# |

|

Unused |

OWS#2 |

8 |

Data1 |

SLBURSTft |

|

+12 В |

+12 В |

9 |

Data 0 |

MSBURST^ |

|

M/-IO |

GND |

10 |

IOCHDRY |

W/R# |

|

-LOCK |

SmemWR# |

11 |

AENx |

GND |

|

Reserved |

SmemRD# |

12 |

Addr19 |

EMB66#3 |

|

GND |

IOWR# |

13 |

Addi-18 |

EMB133#3 |

|

Reserved |

IORD# |

14 |

Addr17 |

Reserved |

|

ВЕЗ" |

DACK3# |

15 |

Addr16 |

GND |

|

Key |

DRQ3 |

16 |

Addr15 |

Key |

|

BE2# |

DACK 1# |

17 |

Addr14 |

BE 1# |

|

BEO# |

DRQ1 |

18 |

Addr13 |

LA 31^ |

|

GND |

Refr" |

19 |

Addr12 |

GND |

|

+5 В |

Bclock |

20 |

Addr11 |

LA30# |

|

LA29# |

IRQ 7 |

21 |

Addr10 |

LA28# |

|

GND |

IRQ 6 |

22 |

Addr 9 |

LA27# |

|

LA26# |

IRQ 5 |

23 |

Addr 8 |

LA25# |

|

LA24# |

IRQ 4 |

24 |

Addr 7 |

GND |

|

Key |

IRQ3 |

25 |

Addr 6 |

Key |

|

LA 16 |

DACK2# |

26 |

Addr 5 |

LA 15 |

|

LA 14 |

TC |

27 |

Addr 4 |

LA 13 |

|

+5 В |

BALE |

28 |

Addr3 |

LA 12 |

|

+5 В |

+5 В |

29 |

Addr 2 |

LA11 |

|

GND |

Osc. |

30 |

Addr1 |

GND |

|

LA 10 |

GND |

31 |

AddrO |

LA9 |

'B4: XT=IRQ2, AT-IRQ9.

^8: XT-Card Selected.

^12, E13 - только для Fast EISA.

|

РядН |

Ряд О |

N# |

РядС |

Рядб |

|

LA8 |

MCS16# |

1 |

SBHE# |

LA7 |

|

LA6 |

IOCS16# |

2 |

LA 23 |

GND |

|

LA5 |

IRQ 10 |

3 |

LA 22 |

LA4 |

|

+5 В |

IRQ 11 |

4 |

LA 21 |

LA3 |

|

LA2 |

IRQ 12 |

5 |

LA 20 |

GND |

|

Key |

IRQ 15 |

6 |

LA 19 |

Key |

|

Data 16 |

IRQ 14 |

7 |

LA 18 |

Data 17 |

|

Data 18 |

DACKO# |

8 |

LA 17 |

Data 19 |

|

GND |

DRQO |

9 |

MemRD# |

Data 20 |

|

Data 21 |

DACK5^ |

10 |

MemWR* |

Data 22 |

|

Data 23 |

DRQ5 |

11 |

Data 8 |

GND |

|

Data 24 |

DACK6# |

12 |

Data 9 |

Data 25 |

|

GND |

DRQ6 |

13 |

Data 10 |

Data 26 |

|

Data 27 |

DACK7# |

14 |

Data 11 |

Data 28 |

|

Key |

DRQ7 |

15 |

Data 12 |

Key |

|

Data 29 |

+5 В |

16 |

Data 13 |

GND |

|

+5 В |

Master* |

17 |

Data 14 |

Data 30 |

|

+5 В |

GND |

18 |

Data 15 |

Data 31 |

|

МАКх# |

- |

19 |

- |

MREQx |

Сигналы шины ISA восходят к шинам Microbus и Multibus,

они естественны для периферийных микросхем фирмы Intel

для процессоров 8080 и 80х86/88. Набор сигналов ISA-8 пре-

дельно прост. Программное обращение к ячейкам памяти и

пространства ввода/вывода обеспечивают следующие сигналы:

^ Data[7:0] - шина данных.

^ Addr[19:0] -шина адреса.

т AEN - разрешение адресации портов (запрещает ложную

дешифрацию адреса в цикле DMA).

^ IOWR# - запись в порт.

^ IORD# - чтение порта.

^ SMemWR-ft - запись в память

(в диапазоне адресов 0-FFFFFh).

^ SMemRD# - чтение памяти

(в диапазоне адресов 0-FFFFFh).

К сигналам запросов прерывания и каналам прямого доступа

к памяти относятся следующие:

йй IRQ2/9, IRQ[3:7] - запросы прерываний. Положительный

перепад сигнала вызывает запрос аппаратного прерыва-

ния. Для идентификации источника высокий уровень

должен сохраняться до подтверждения прерывания про-

цессором, что затрудняет разделяемое использование пре-

рываний. Линия IRQ2/9 в шинах XT вызывает аппарат-

ное прерывание с номером 2, а в AT - с номером 9.

^ DRQ[1:3] - запросы 8-битных каналов DMA (положитель-

ным перепадом).

т DACK[1:3]# - подтверждение запросов 8-битных каналов

DMA.

^ ТС - признак завершения счетчика циклов DMA.

Шина имеет и несколько служебных сигналов синхрониза-

ции, сброса и регенерации памяти, установленной на адап-

терах:

ш IOCHRDY - готовность устройства, низкий уровень удли-

няет текущий цикл (не более 15 мкс).

^ BALE - разрешение защелки адреса. После его спада в

каждом цикле процессора линии Addr 0-19 гарантиро-

ванно содержат действительный адрес.

^ Refr# - цикл регенерации памяти (в XT называется

DACK 0#). Сигнал появляется каждые 15 мкс, при этом

шина адреса указывает на очередную регенерируемую

строку памяти.

т 10СНК - контроль канала. Низкий уровень сигнала вы-

зывает NMI CPU (разрешение и индикация в системных

портах 061h, 062h).

^ Reset - сигнал аппаратного сброса (активный уровень -

высокий).

^ BCIock - синхронизация шины с частотой около 8 МГц.

ПУ могут не использовать этот сигнал, работая только

по управляющим сигналам записи и чтения.

т OSC - частота 14,431818 МГц, несинхронизированная с ши-

ной (использовалась старыми дисплейными адаптерами).

Кроме логических сигналов шина имеет контакты для раз-

водки питания +5, -5, +12 и -12В.

Дополнительный разъем, расширяющий шину до 16-битной,

содержит линии данных, адреса, запросов прерываний и ка-

налов прямого доступа:

as Data[15:8] -шина данных.

^ SB HE - признак наличия данных на линиях Data [15:8].

^ LA[23:17j - нефиксированные сигналы адреса, требующие

защелкивания по спаду сигнала BALE. Такой способ по-

дачи адреса позволяет сократить время цикла (схемы де-

шифратора адреса памяти плат расширения начинают де-

кодирование несколько раньше спада BALE).

т IRQ[10:12], IRQ[14:15] - дополнительные запросы преры-

ваний.

^ DRQ[5:7] - запросы 16-битных каналов DMA (положи-

тельным перепадом).

т DACK[5:7]# - подтверждение запросов 16-битных каналов

DMA.

С переключением разрядности данных связаны сигналы:

^ MCS16# - адресуемое устройство поддерживает 16-бит-

ные обращения к памяти.

^ IOCS16# - адресуемое устройство поддерживает 16-бит-

ные обращения к портам.

К новым управляющим сигналам относятся следующие:

^ MemWR# - запись в память в любой области до

16 Мбайт.

^ MemRD# - чтение памяти в любой области до 16 Мбайт.

^ OWS# - сигнал от устройства, разрешающий системной пла-

те укоротить текущий цикл (устранить такты ожидания).

^ MASTERS - запрос от устройства, использующего 16-бит-

ный канал DMA на управление шиной. При получении

подтверждения DACK [5:7] Bus-Master может захватить

шину (не более чем на 15 мкс).

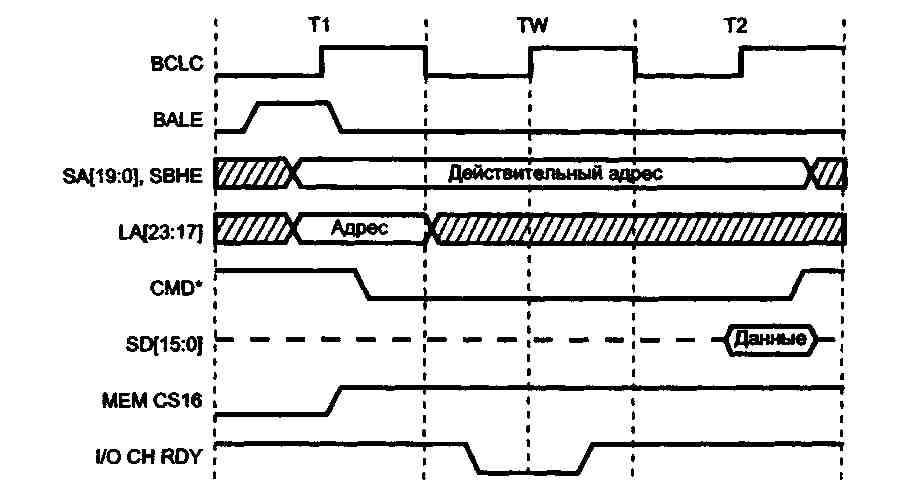

Обобщенные временные диаграммы циклов чтения или за-

писи памяти или ввода/вывода приведены на рис. 4.5. Здесь

условный сигнал CMD* изображает один из сигналов:

^ SMEMRD#, MEMRD# - в цикле чтения памяти;

s SMEMWR#, MEMWR# - в цикле записи памяти;

^ IORD# - в цикле чтения порта ввода/вывода;

^ IOWR# - в цикле записи порта ввода/вывода.

Рис. 4.5. Временные диаграммы циклов чтения или записи

на шине ISA

В каждом из рассматриваемых циклов активными (с низ-

ким уровнем) могут быть только сигналы лишь из одной

строки данного списка. Цикл прямого доступа к памяти, в

котором это правило не соблюдается, рассмотрен в прило-

жении А (см. рис. А.2).

По адресованному ему спаду сигнала чтения устройство долж-

но выдать на шину данных содержимое адресуемой ячейки

и удерживать его, пока не произойдет подъем сигнала. Во

время циклов записи процессор выставляет действительные

данные несколько позже начала (спада) сигнала записи. Уст-

ройство должно фиксировать для себя эти данные в конце

цикла по подъему сигнала. Обращение к портам ввода/вы-

вода отличается тем, что сигналы LA[32:17] не используются.

Минимальная длительность цикла определяется чипсетом и

может программироваться опциями BIOS Setup заданием

тактов ожидания. При этом циклы обращения к памяти ко-

роче циклов обращения к портам ввода/вывода. В шине AT

для управления минимальной длительностью цикла исполь-

зуются также сигналы управления разрядностью передачи:

если устройство поддерживает 16-битные передачи, предпо-

лагается, что оно может работать с меньшим количеством

тактов ожидания. Этим объясняется, что в Setup длитель-

ности циклов ISA задаются раздельно как для памяти и вво-

да/вывода, так и для 8- и 16-битных операций.

Если устройство не работает с заданными циклами, оно мо-

жет вводить дополнительные такты ожидания, используя

сигнал IOCHRDY, но при этом недопустимо удлинять цикл

более чем на 15 мкс.

Шина EISA позволяет устройствам работать как в режиме

ISA, так и в новых режимах EISA. Из сигналов ISA исполь-

зуются линии адреса/данных с расширением их до 32 бит,

сигналы прерываний и прямого доступа к памяти и синхро-

низации. Для своих циклов обмена EISA использует соб-

ственный набор управляющих сигналов с обязательной син-

хронизацией по сигналу BCLK. Сигналы IORD# и IOWR# при

обращении к EISA-портам не используются. Вместо них при-

меняются сигналы обращения М/10# и W/R#. В EISA-цик-

лах не используется сигнал SBHE; он заменен сигналами раз-

решения байт ВЕ[3:0]. Вместо общего сигнала AEN каждый

слот имеет собственный сигнал AENx. К сигналам расшире-

ния шины EISA относятся следующие:

^ LA[23:16] - опережающие сигналы адреса, требующие за-

щелкивания по спаду сигнала BALE.

ж LA[31:24]# - аналогично LA [2:23], но с инверсией.

^ ВЕ[3:0]# - индикаторы действительности данных в бай-

тах 0-3 при EISA-цикле.

^ М/Ю# - обращение к памяти (1) или портам (0) EISA.

m W/R# - запись (1) или чтение (0) EISA.

^ ЕХ16#, ЕХ32# - индикаторы разрядности ресурсов.

т SI-BURSTS - адресуемое устройство поддерживает пакет-

ный режим обмена.

ж MSBURST^ - уведомление устройства, подавшего сигнал

SLBURST, о намерении инициировать пакетный обмен.

ва LOCK# - обеспечение исключительного права доступа

активного EISA Bus-Master к памяти или портам.

ss EXRDY - готовность EISA-устройства; аналогично сигна-

лу IOCHRDCY.

^ STARTS - отмечает начало цикла EISA-доступа. Во вре-

мя действия этого сигнала фиксируется адрес и опреде-

ляется тип обращения.

^ CMD# - задает временные параметры цикла; действует

после сигнала STARTS.

^ MREQx# - EISA Bus-Master слота "х" запрашивает

управление шиной.

^ МАКх# - EISA Bus-Master слота "х" получает управле-

ние шиной от арбитра.

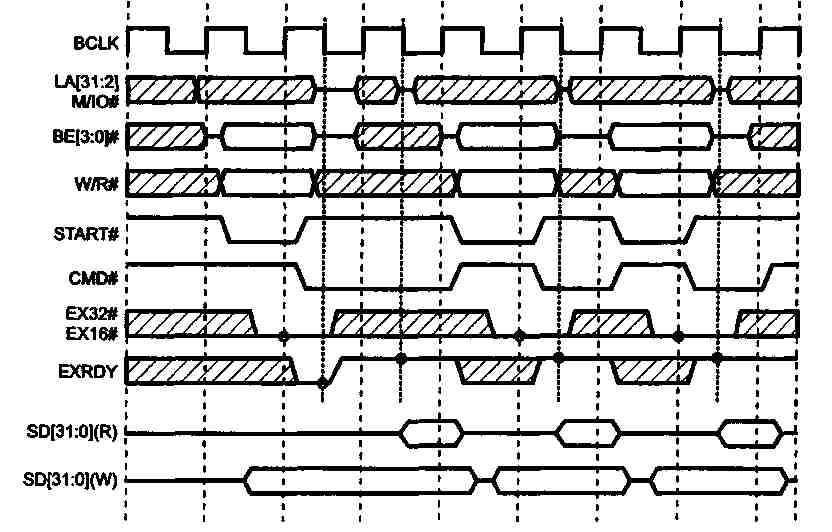

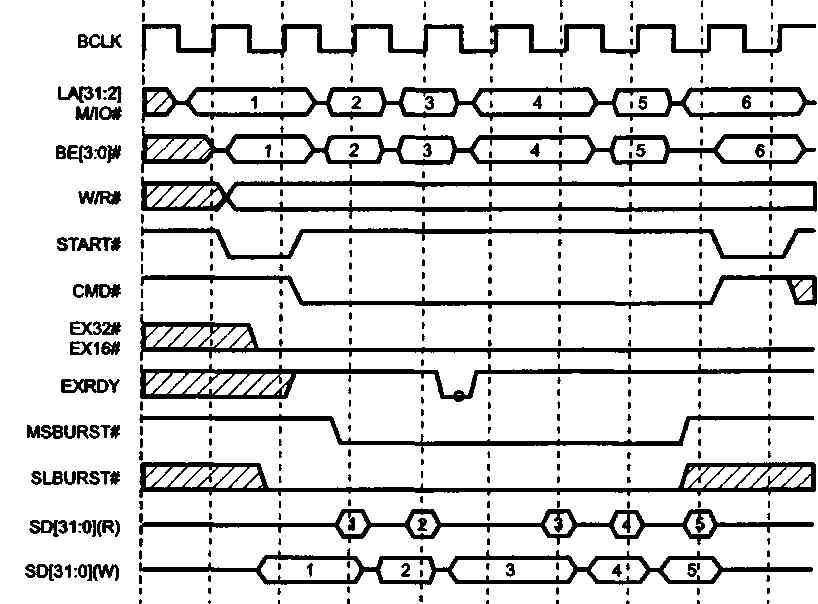

Рис. 4.6. Временные диаграммы одиночных циклов на шине EISA

Рис. 4.7. Временные диаграммы пакетных циклов на шине EISA

Временные диаграммы одиночных и пакетных циклов об-

мена по шине EISA приведены на рис. 4.6 и 4.7. Обратим

внимание на то, что действительные значения сигналов дол-

жны фиксироваться по положительному перепаду BCLKft, a

готовность проверяется по отрицательному.

Для шин ISA ряд фирм выпускают карты-прототипы

(Prototype Card), представляющие собой печатные платы

полного или уменьшенного формата с крепежной скобой. На

платах установлены обязательные интерфейсные цепи - бу-

фер данных, дешифратор адреса и некоторые другие. Осталь-

ная часть платы свободна, и здесь разработчик может раз-

местить макетный вариант своего устройства. Эти платы

удобны для проверки нового изделия, а также для монтажа

единичных экземпляров устройства, когда разработка и из-

готовление печатной платы нерентабельно.

На некоторых системных платах (ASUSTek) имеется неболь-

шой разъем с загадочным названием Media Bus, расположен-

ный позади разъема шины PCI одного из слотов. На этот

разъем выводятся сигналы шины ISA. Он предназначен для

того, чтобы на графическом адаптере с шиной PCI можно было

разместить недорогой чипсет звуковой карты, предназначен-

ный для шины ISA. Этот разъем и такие комбинированные

аудиовидеокарты широкого распространения не получили.

Обычно в PC разъемы шины расширения устанавливают на

системную плату. Для компьютеров инструментального и

промышленного назначения по ряду причин удобнее исполь-

зовать модули, соединяемые пассивной объединяющей пла-

той. Самый простой соответствующий конструктив заклю-

чается в использовании стандартной шины и карты ISA. Все

компоненты с традиционной системной платы перенесли на

карту ISA, получив одноплатный компьютер, называемый

микроРС (mPC - microPC). На такой карте содержатся про-

цессор, память, графический адаптер, контроллеры портов

и дисковые интерфейсы, иногда дополнительные контрол-

леры цифрового и аналогового ввода/вывода. Для подклю-

чения к модулям расширения используют пассивную кросс-

плату с обычными разъемами ISA. Если требуется более

высокопроизводительный канал, применяют шину PCI. При

этом на плате системного контроллера присутствуют два

краевых разъема - ISA на обычном месте и PCI примерно

на том месте, где располагался разъем VLB. Кросс-плата для

таких систем становится неоднородной - часть ее слотов

имеет разъемы PCI, другая часть - ISA, место для систем-

ного контроллера оборудовано обоими разъемами.

Логически эквивалентной ISA является шина PC-104, предна-

значенная для построения встраиваемых контроллеров. 104 -

число контактов коннектора, на который выводятся сигналы

шины ISA. От ISA шина PC-104 отличается только типом

коннектора и нагрузочными характеристиками линий. Осно-

вой контроллера является mPC с разъемом PC-104 (розетка).

Если требуется подключение платы расширения, она своей

вилкой PC-104 вставляется в плату контроллера. Кроме вил-

ки на плате расширения имеется розетка PC-104 (коннектор

двухсторонний), так что можно собрать "бутерброд" из не-

скольких плат. Если плат более трех, то сверху "бутерброда"

устанавливают терминатор. Для фиксации плат стандартизо-

вано расположение крепежных отверстий. Платы скрепляют-

ся несущими стойками (длинными винтами со втулками).

4.2. Шина МСА

МСА (MicroChannel Architecture) - микроканальная архи-

тектура - была введена фирмой IBM для своих компьюте-

ров PS/2, начиная с модели 50. Шина МСА абсолютно не-

совместима с ISA/EISA. Состав управляющих сигналов,

протокол и архитектура ориентированы на асинхронное

функционирование шины и процессора, что снимает про-

блемы согласования скоростей процессора и ПУ. Архитек-

тура позволяет эффективно и автоматически конфигуриро-

вать все устройства программным путем (в картах МСА нет

ни одного переключателя).

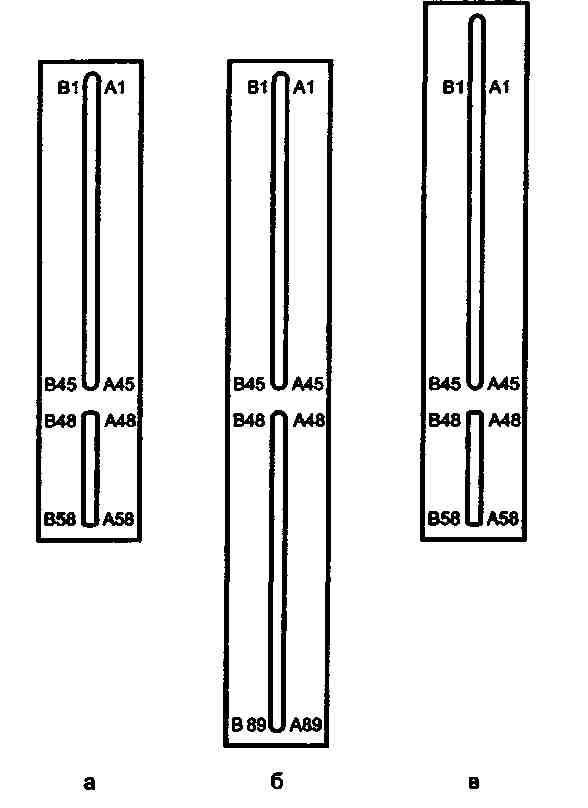

Слоты МСА имеют контакты с шагом 0,05 дюйма. Число сло-

тов на системной плате зависит от модели компьютера.

Рис. 4.8. Слоты МСА: а - 16-битный, б - 32-битный,

в - 16-битный с расширением

§? 16-битный слот (рис. 4.8а) использует контакты А1/В1-

А45/В45 для 8-битных операций и А48/В48-А58/В58

для 16-битных. Пропущенные номера 46, 47 - ключ для

всех слотов.

§* 32-битный слот (рис. 4.86) имеет удлиненную вторую

секцию с контактами А48/В48-А89/В89.

Перед контактами А1/В1 возможно одно из двух расшире-

ний за счет удлинения первой секции (рис. 4.8в):

ж АМ1/ВМ1-АМ4/ВМ4 - для плат расширения памяти;

т AV1/BV1-AV10/BV10 - для плат видеоадаптеров. Позво-

ляет использовать общие цепи встроенного в системную

плату VGA-адаптера, теоретически удешевляя расшире-

ние видеосистемы. По составу сигналов видеорасшире-

ние близко к разъему VGA Auxiliary Video Connector или

VESA Feature Connector.

При всей прогрессивности архитектуры МСА не пользуется

популярностью, в частности, из-за полной несовместимости

с ISA. МСА находит применение в мощных файл-серверах,

где требуется высоконадежный производительный ввод/

вывод.

4.3. Локальная шина VLB

Шины ввода/вывода ISA, МСА, EISA имеют низкую

производительность, обусловленную их ролью в структуре

PC. Современные приложения требуют существенного по-

вышения пропускной способности шины. Одним из реше-

ний проблемы стало применение локальной шины процес-

сора 486. Шину процессора использовали как место

подключения периферии (контроллера дисков и графичес-

кого адаптера).

VLB (VESA Local Bus) - стандартизованная 32-битная ло-

кальная шина, практически представляющая собой сигналы

системной шины процессора 486, выведенные на дополни-

тельные разъемы системной платы. Шина ориентирована

на процессор 486, хотя возможно ее использование с 386. Для

процессоров Pentium была принята спецификация 2.0, в ко-

торой разрядность шины данных увеличена до 64, но она

распространения не получила.

Конструктивно VLB-слот аналогичен 16-битному МСА-сло-

ту, но является расширением системного слота шины ISA-

16, EISA или МСА, располагаясь позади него вблизи от

процессора. Из-за ограниченной нагрузочной способности

шины процессора больше трех слотов VLB на системной

плате не устанавливают. Максимальная тактовая частота

шины - 66 МГц, хотя шина работает надежнее на частоте

33 МГц. Декларируется пиковая пропускная способность

132 Мбайт/с (33 МГцх4 байта), но она достигается только

при пакетной передаче. Реально в пакетном цикле передача

4х4 = 16 байт данных требует 5 тактов шины, так что даже

в нем пропускная способность составляет 105,6 Мбайт/с, а

в обычном режиме (по такту на фазу адреса и на фазу дан-

ных) - 66 Мбайт/с. Жесткие требования к временным ха-

рактеристикам процессорной шины при большой нагрузке

(со стороны микросхем внешнего кэша) могут привести к

неустойчивой работе: все три VLB-слота могут использо-

ваться только на частоте 40 МГц. При нагруженной сис-

темной плате на 50 МГц может работать только один слот.

Шина допускает применение активных (Bus-Master) адап-

теров, но арбитраж запросов возлагается на сами адапте-

ры. Разрешена установка не более двух Bus-Master-адапте-

ров, один из которых устанавливается в "Master"-слот.

Шину VLB использовали для подключения графического

адаптера и контроллера дисков. Встречаются системные пла-

ты, которые имеют встроенный графический и дисковый

адаптеры с шиной VLB, но самих слотов VLB нет. Это озна-

чает, что на плате установлены микросхемы указанных адап-

теров для шины VLB. Такая неявная шина по производи-

тельности не уступает обычной, а с точки зрения надежности

и совместимости она даже лучше.

Назначение контактов шины VLB представлено в табл. 4.4.

В названиях сигналов можно узнать сигналы процессо-

ра 486.

|

Ряд В |

№ |

РЯДА |

||

|

32/64- |

64-битный |

|

32/64-битный |

64-битный |

|

Data 0 |

- |

1 |

Data1 |

- |

|

Data 2 |

- |

2 |

Data3 |

- |

|

Data 4 |

- |

3 |

GND |

- |

|

Data 6 |

- |

4 |

Data 5 |

- |

|

Data 8 |

- |

5 |

Data 7 |

- |

|

GND |

- |

6 |

Data 9 |

- |

|

Data 10 |

- |

7 |

Data 11 |

- |

|

Data 12 |

- |

8 |

Data 13 |

- |

|

VCC |

- |

9 |

Data 15 |

- |

|

Data 14 |

- |

10 |

GND |

- |

|

Data 16 |

- |

11 |

Data 17 |

- |

|

Data 18 |

- |

12 |

VCC |

- |

|

Data 20 |

- |

13 |

Data 19 |

- |

|

GND |

- |

14 |

Data 21 |

- |

|

Data 22 |

- |

15 |

Data 23 |

- |

|

Data 24 |

- |

16 |

Data 25 |

- |

|

Data 26 |

- |

17 |

GND |

- |

|

Data 28 |

- |

18 |

Data 27 |

- |

|

Data 30 |

- |

19 |

Data 29 |

- |

|

VCC |

- |

20 |

Data 31 |

- |

|

Addr31 |

Data 63 |

21 |

Addr30 |

Data 62 |

|

GND |

- |

22 |

Addr28 |

Data 60 |

|

Addr29 |

Data 61 |

23 |

Addr26 |

Data 58 |

|

Addr27 |

Data 59 |

24 |

GND |

- |

|

Addr25 |

Data 57 |

25 |

Addr24 |

Data 56 |

|

Addr23 |

Data 55 |

26 |

Addr 22 |

Data 54 |

|

Addr21 |

Data 53 |

27 |

VCC |

- |

|

Ряд В |

№ |

РЯДА |

||

|

32/64- |

64-битный |

|

32/64-битный |

64-битный |

|

Addr19 |

Data 51 |

28 |

Addr 20 |

Data 52 |

|

GND |

- |

29 |

Addr 18 |

Data 50 |

|

Addr17 |

Data 49 |

30 |

Addr16 |

Data 48 |

|

Addr 15 |

Data 47 |

31 |

Addr 14 |

Data 46 |

|

VCC |

- |

32 |

Addr 12 |

Data 44 |

|

Addr13 |

Data 45 |

33 |

Addr 10 |

Data 42 |

|

Addr11 |

Data 43 |

34 |

Addr 8 |

Data 40 |

|

Addr 9 |

Data 41 |

35 |

GND |

- |

|

Addr 7 |

Data 39 |

36 |

Addr 6 |

Data 38 |

|

Addr 5 |

Data 37 |

37 |

Addr 4 |

Data 36 |

|

GND |

- |

38 |

Write Back |

- |

|

Addr3 |

Data 35 |

39 |

Byte Enable 0 |

Byte |

|

Addr 2 |

Data 34 |

40 |

VCC |

- |

|

Unused |

LBS64* |

41 |

Byte Enable 1 |

Byte |

|

Reset |

- |

42 |

Byte Enable 2 |

Byte |

|

Data-Code |

- |

43 |

GND |

- |

|

Mem-l/0 |

Data 33 |

44 |

Byte Enable 3 |

Byte |

|

Wr-Rd Status |

Data 32 |

45 |

Address Data |

- |

|

ключ |

- |

46 |

ключ |

- |

|

ключ |

- |

47 |

ключ |

- |

|

Ready Return |

- |

48 |

Local Ready |

- |

|

GND |

- |

49 |

Local Device |

- |

|

IRQ 9 |

- |

50 |

Local Request |

- |

|

Burst Ready |

- |

51 |

GND |

- |

|

Burst Last |

- |

52 |

Local Bus Grant |

- |

|

Ряд В |

№ |

РЯДА |

||

|

32/64- |

64-битный |

|

32/64-битный |

64-битный |

|

ID 0 |

- |

53 |

VCC |

- |

|

ID1 |

- |

54 |

ID 2 |

- |

|

GND |

- |

55 |

IDS |

- |

|

Local Clock |

- |

56 |

ID 4 |

ACK64# |

|

VCC |

- |

57 |

Unused |

- |

|

Local Bus |

^~ |

58 |

Loc/Ext |

"~ |

4.4. Шина PCI

PCI (Peripheral Component Interconnect) local bus - шина со-

единения периферийных компонентов. Будучи локальной, эта

шина занимает особое место в современной архитектуре PC,

являясь мостом (mezzanine bus) между системной шиной про-

цессора и шиной ввода/вывода ISA/EISA или МСА. Шина

PCI разрабатывалась в расчете на Pentium-системы, но хоро-

шо сочетается и с процессорами 486. Является четко стандар-

тизованной высокопроизводительной и надежной шиной рас-

ширения. В настоящее время действует спецификация PCI 2.1.

При частоте шины 33 МГц скорость теоретически достигает

132/264 Мбайт/с для 32/64 бит; при частоте синхронизации

66 МГц - в два раза выше (версия 2.1 допускает частоту до

66 МГц при согласии всех устройств на шине).

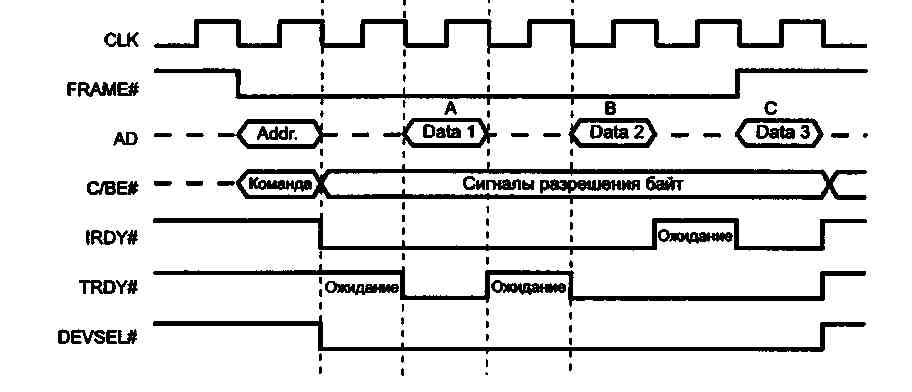

Шина является синхронной - фиксация всех сигналов вы-

полняется по положительному перепаду (фронту) сигнала

CLK. В каждой транзакции (обмене по шине) участвуют два

устройства - инициатор обмена (Initiator или Master, ини-

циирующее устройство, ИУ) и целевое устройство (Target

или Slave, ЦУ).

Шина PCI все транзакции трактует как пакетные: каждая

транзакция начинается фазой адреса, за которой может сле-

довать одна или несколько фаз данных. Для адреса и дан-

Hbix используются общие мультиплексированные линии AD.

Четыре мультиплексированные линии С/ВЕ[3:0] использу-

ются для кодирования команд в фазе адреса и разрешения

байт в фазе данных. В начале транзакции И У активизирует

сигнал FRAME#, по шине AD передает целевой адрес, а по

линиям С/ВЕ# - информацию о типе транзакции (коман-

де). Адресованное ЦУ отзывается сигналом DEVSEL#, после

чего И У может указать на свою готовность к обмену данны-

ми сигналом IRDY#. Когда к обмену данными будет готово и

ЦУ, оно установит сигнал TRDY#. Данные по шине AD могут

передаваться только при одновременном наличии сигналов

IRDYft и TRDY#. С помощью этих сигналов ИУ и ЦУ согла-

суют свои скорости, вводя такты ожидания. На рис. 4.9 при-

ведена временная диаграмма обмена, в которой и ИУ, и ЦУ

вводят такты ожидания. Если бы они оба ввели сигналы го-

товности в конце фазы адреса и не снимали их до конца

обмена, то в каждом такте после фазы адреса передавались

бы по 32 бита данных, что обеспечило бы выход на предель-

ную производительность обмена.

Рис. 4.9. Цикл обмена на шине РС1

Количество фаз (циклов) данных в пакете заранее не опре-

делено, но перед последним циклом ИУ при введенном сиг-

нале IRDY# снимает сигнал FRAMED. После последней фазы

данных ИУ снимает сигнал IRDY#, и шина переходит в со-

стояние покоя (PCI Idle) - оба. сигнала FRAME# и IRDY# на-

ходятся в пассивном состоянии. Максимальное количество

циклов данных в пакете может быть неявно ограничено тай-

мером, определяющим максимальное время, в течение кото-

рого И У может пользоваться шиной. И У завершает тран-

закцию одним из следующих способов:

^ Нормальное завершение выполняется по окончании об-

мена данными.

^ Завершение по тайм-ауту (Time-out) происходит, когда

во время транзакции у ИУотбирают право на управле-

ние шиной (снятием сигнала GNT#) или когда истекает

время, указанное в его таймере MLT (медленное ЦУ или

слишком длинная транзакция).

^ Транзакция отвергается (Abort), когда в течение заданно-

го времени ИУ не получает ответа ЦУ (DEVSEL#).

Транзакция может быть прекращена и по инициативе ЦУ,

для этого оно может ввести сигнал STOP#. Возможны три

типа прекращения:

^ Отключение (Disconnect) - сигнал STOP# вводится во

время активности TRDY#. В этом случае транзакция за-

вершается после фазы данных.

^ Отключение с повтором (Disconnect/Retry) - сигнал

STOP# вводится при пассивном состоянии TRDY#, и по-

следняя фаза данных отсутствует. Является указанием ИУ

на необходимость повтора транзакции.

^ Отказ (Abort) - сигнал STOP# вводится одновременно со

снятием DEVSEL# (в предыдущих случаях во время по-

явления сигнала STOP# сигнал DEVSEL^ был активен). В

этом случае последняя фаза данных тоже отсутствует, но

повтор не запрашивается.

Протокол квитирования обеспечивает надежность обмена -

ИУ всегда получает информацию об отработке транзакции

ЦУ. Средством повышения надежности (достоверности) яв-

ляется применение контроля паритета: линии AD[31:0] и

С/ВЕ#[3:0] и в фазе адреса, и в фазе данных защищены битом

паритета PAR (количество единичных бит этих линий, вклю-

чая PAR, должно быть четным). Действительное значение PAR

появляется на шине с задержкой в один такт относительно

линий AD и С/ВЕ#. При обнаружении ошибки ЦУ со сдви-

том на такт вырабатывается сигнал PERFW. В подсчете пари-

тета при передаче данных учитываются все байты, включая

и недействительные (отмеченные высоким уровнем сигнала

C/BE#i). Состояние бит и недействительных байт данных во

время фазы данных должно оставаться стабильным.

Арбитражем запросов на использование шины занимается

специальный узел, входящий в чипсет системной платы. Каж-

дое ИУ имеет пару сигналов - REQft для запроса на управ-

ление шиной и GNT# для подтверждения предоставления

управления шиной. Схема приоритетов (фиксированный,

циклический, комбинированный) определяется программи-

рованием арбитра.

Каждое устройство - потенциальное ИУ (PCIMaster) - име-

ет собственный программируемый таймер MLT (Master

Latency Timer), определяющий максимальное количество так-

тов шины, допустимое для одной транзакции. Его конфигу-

рированием осуществляется распределение полосы пропус-

кания шины между устройствами.

Каждое ЦУ имеет инкрементный механизм слежения за дли-

тельностью циклов (Incremental Latency Mechanism), который

не позволяет интервалу между соседними фазами данных в

пакете превышать 8 тактов шины. Если ЦУ не успевает ра-

ботать в таком темпе, оно обязано остановить транзакцию.

Адресация памяти, портов и конфигурационных регистров

различна. Байты шины AD, несущие действительную инфор-

мацию, выбираются сигналами С/ВЕ[3:0] в фазах данных

(внутри пакета эти сигналы могут менять состояние). В цик-

лах обращения к памяти адрес, выровненный по границе

двойного слова, передается по линиям AD[31:2], линии

AD[1:0] задают порядок чередования адресов в пакете:

^ 00 - линейное инкрементирование;

^ 01 - чередование адресов с учетом длины строки кэш-

памяти;

^ 1х -зарезервировано.

В циклах обращения к портам ввода/вывода для адресации

любого байта используются все линии AD[31:0]. В циклах

конфигурационной записи/считывания устройство выбира-

ется индивидуальным сигналом IDSEL#, конфигурационные

регистры выбираются двойными словами по линиям AD[7:2],

при этом AD[1:0]=00. Сигнал выборки IDSEL# воспринима-

ется устройством только в фазе адреса, поэтому обычно в

качестве него используют старшие биты адреса с позицион-

ным кодированием адреса устройства.

Команды шины PCI определяются значениями бит С/ВЕ# в

фазе адреса в соответствии с табл. 4.5.

|

С/ВЕ[3:0] |

Тип команды |

|

0000 |

Interrupt Acknowledge - подтверждение прерывания |

|

0001 |

Special Cycle - специальный цикл |

|

0010 |

I/O Read - чтение порта ввода/вывода |

|

0011 |

I/O Write - запись в порт ввода/вывода |

|

0100 |

Зарезервировано |

|

0101 |

Зарезервировано |

|

0110 |

Memory Read - чтение памяти |

|

0111 |

Memory Write - запись в память |

|

1000 |

Зарезервировано |

|

1001 |

Зарезервировано |

|

1010 |

Configuration Read - конфигурационное считывание |

|

1011 |

Configuration Write - конфигурационная запись |

|

1100 |

Multiple Memory Read - множественное чтение памяти |

|

1101 |

Dual Address Cycle - двухадресный цикл |

|

1110 |

Memory Read Line - чтение строк памяти |

|

1111 |

Memory Write and Invalidate - запись с инвалидацией |

В команде подтверждение прерывания контроллер прерыва-

ний передает вектор прерывания по шине AD.

Специальный цикл декодируется содержимым линий AD[15:0]

и используется для указания на отключение (Shutdown), ос-

танов (Halt) процессора или специфические функции процес-

сора, связанные с кэшем и трассировкой. Этим состояниям

соответствуют коды 0000, 0001 и 0002; коды 0003-FFFFh за-

резервированы.

В командах чтения и записи ввода/вывода линии AD содер-

жат адрес байта, причем декодированию подлежат и биты

ADO и AD1 (несмотря на то, что имеются сигналы ВЕх#).

Порты PCI могут быть 8-, 16- или 32-битными. Для адреса-

ции портов на шине PCI доступны все 32 бита адреса, но

процессоры х86 могут использовать только младшие 16 бит.

Порты с адресами OCF8 и OCFC зарезервированы под реги-

стры адреса и данных для доступа к конфигурационному

пространству. Обращение к порту данных приведет к гене-

рации шинного цикла конфигурационного чтения или за-

писи по предварительно записанному адресу.

В командах чтения и записи памяти шина AD содержит ад-

реса двойных слов, и линии ADO, AD1 не должны декодиро-

ваться - на конкретные байты указывают сигналы С/

ВЕ[3:0]#.

Команды конфигурационного чтения и записи адресуются к

конфигурационному пространству и обеспечивают доступ

к 256-байтным структурам. Обращение производится двой-

ными словами. Структура содержит идентификатор устрой-

ства и производителя, состояние и команду, информацию об

используемых ресурсах и ограничения на использование

шины.

Множественное чтение памяти используется для транзак-

ций, пересекающих границы строк кэш-памяти.

Двухадресный цикл применяется, когда физическая шина

имеет 32 бита адреса, а требуется передача с 64-битной ад-

ресацией. В этом случае младшие 32 бита адреса передают-

ся в цикле данного типа, а за ним следует обычный цикл,

определяющий тип обмена и несущий старшие 32 бита ад-

реса. Шина PCI допускает 64-битную адресацию даже для

портов ввода/вывода (для х86 это бесполезно, но PCI суще-

ствует и на других платформах).

Чтение строк памяти применяется, когда в транзакции пла-

нируется более двух 32-битных передач (обычно это чтение

до конца строки кэша).

Запись с инвалидацией применяется к целым строкам кэша

и позволяет оптимизировать циклы обратной записи "гряз-

ных" строк кэша.

Выделение специальных циклов множественного чтения,

чтения строк и записи с инвалидацией позволяет контрол-

леру памяти предпринять определенные меры для оптими-

зации данных передач.

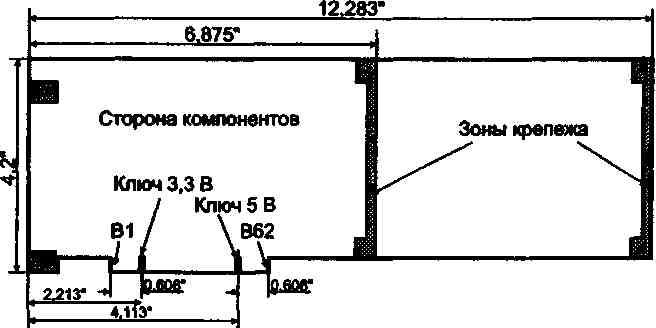

Слоты PCI с шагом 0,05 дюйма расположены несколько даль-

ше от задней панели, чем ISA/EISA или МСА. Компоненты

карт PCI расположены на левой поверхности плат. По этой

причине крайний PCI-слот обычно разделяет использование

посадочного места адаптера с соседним ISA-слотом (Shared

slot). Шина имеет версии с питанием 5 В, 33 В и универ-

сальную (с переключением линий +V I/O с 5 В на 3,3 В). Клю-

чами являются пропущенные ряды контактов 12, 13 и 50, 51.

Для слота на 5 В ключ расположен на месте контактов 50, 51;

для 3 В - 12, 13; для универсального - два ключа: 12, 13

и 50, 51. Ключи не позволяют установить карту в слот с не-

подходящим напряжением питания, 32-битный слот закан-

чивается контактами А62/В62, 64-битный - А94/В94. На

рис. 4.10 изображена 32-битная плата максимального размера

(Long Card), длина короткой платы (Short Card) - 6,875".

Плата может иметь обрамление (скобки), стандартное для

конструктива ISA или МСА. Назначение выводов универ-

сального разъема приведено в табл. 4.6, назначение сигна-

лов - в табл. 4.7.

Рис. 4.10. Карта расширения для шины PCI

На одной шине PCI может быть не более четырех устройств

(следовательно, и слотов). Для подключения к другим ши-

нам применяются специальные аппаратные средства - мос-

ты PCI (PCI Bridge). Главный мост (Host Bridge) использу-

ется для подключения PCI к системной шине. Одноранго-

вый мост (Peer-to-Peer Bridge) используется для соединения

двух шин PCI. Несколько шин PCI применяются в серве-

рах - это позволяет увеличить число подключаемых уст-

ройств. Для подключения шин ISA/EISA используются спе-

циальные мосты, входящие в чипсеты системных плат.

Каждый мост программируется - ему указываются диапа-

зоны адресов пространств памяти и ввода/вывода, отведен-

ные устройствам его шин. Если адрес ЦУ текущей транзак-

ции на одной шине (стороне) моста относится к шине

противоположной стороны, мост перенаправляет транзакцию

на соответствующую шину и выполняет действия по согла-

сованию протоколов шин. Таким образом, совокупность мо-

стов PCI выполняет маршрутизацию (routing) обращений по

связанным шинам. Считается, что устройство с конкретным

адресом может присутствовать только на одной из шин, а

на какой именно, "знают" запрограммированные мосты. Ре-

шать задачу маршрутизации призван также сигнал DEVSEL#.

Обращения, не востребованные абонентами PCI, обычно пе-

ренаправляются на шину ISA/EISA.

|

Ряд В |

Nft |

РЯДА |

Ряд В |

N# |

РЯДА |

|

-12 В |

1 |

TRST# |

PRSNT2# |

11 |

Reserved |

|

тек |

2 |

+12 В |

GND/Ключ |

12 |

GND/Ключ |

|

GND |

3 |

TMS |

GND/Ключ |

13 |

GND/Ключ |

|

TDO |

4 |

TDI |

Reserved |

14 |

Reserved |

|

+5 В |

5 |

+5 В |

GND |

15 |

RST# |

|

+5 В |

6 |

INTRA# |

Clock |

16 |

+VI/0 |

|

INTRB# |

7 |

INTRC# |

GND |

17 |

GNT# |

|

INTRD# |

8 |

+5 В |

REQ# |

18 |

GND |

|

PRSNT1# |

9 |

Reserved |

+VI/0 |

19 |

Reserved |

|

Reserved |

10 |

+VI/0 |

AD 31 |

20 |

AD 30 |

|

Ряд В |

N# |

РЯДА |

Ряд В |

N# |

РЯДА |

|

AD 29 |

21 |

+3,3 В |

GND/Ключ |

50 |

GND/Ключ |

|

GND |

22 |

AD 28 |

GND/Ключ |

51 |

GND/Ключ |

|

AD 27 |

23 |

AD 26 |

AD8 |

52 |

С/ВЕО# |

|

AD 25 |

24 |

GND |

AD7 |

53 |

+3,3 В |

|

+3,3 В |

25 |

AD 24 |

+3,3 В |

54 |

AD 6 |

|

С/ВЕЗ# |

26 |

IDSELff |

AD5 |

55 |

AD 4 |

|

AD 23 |

27 |

+3,3 В |

AD3 |

56 |

GND |

|

GND |

28 |

AD 22 |

GND |

57 |

AD 2 |

|

AD 21 |

29 |

AD 20 |

AD 1 |

58 |

ADO |

|

AD 19 |

30 |

GND |

+VI/0 |

59 |

+VI/0 |

|

+3.3 В |

31 |

AD 18 |

АСК64# |

60 |

REQ64# |

|

AD 17 |

32 |

AD 16 |

+5 В |

61 |

+5 В |

|

С/ВЕ2# |

33 |

+3,3 В |

+5 В |

62 |

+5 В |

|

GND |

34 |

FRAMED |

Конец 32-битного разъема |

||

|

IRDY# |

35 |

GND |

Reserved |

63 |

GND |

|

+3,3 В |

36 |

TRDY# |

GND |

64 |

C/BE7# |

|

DEVSEL# |

37 |

GND |

С/ВЕ6# |

65 |

С/ВЕ5# |

|

GND |

38 |

STOP* |

С/ВЕ4# |

66 |

+VI/0 |

|

LOCK* |

39 |

+3,3 В |

GND |

67 |

PAR64 |

|

PERR# |

40 |

SDONE# |

AD63 |

68 |

AD 62 |

|

+3,3 В |

41 |

SDOFF^ |

AD61 |

69 |

GND |

|

SERR# |

42 |

GND |

+VI/0 |

70 |

AD 60 |

|

+3,3 В |

43 |

PAR |

AD59 |

71 |

AD 58 |

|

С/ВЕ1# |

44 |

AD 15 |

AD57 |

72 |

GND |

|

AD 14 |

45 |

+3,3 В |

GND |

73 |

AD 56 |

|

GND |

46 |

AD 13 |

AD55 |

74 |

AD 54 |

|

AD 12 |

47 |

AD 11 |

AD53 |

75 |

+VI/0 |

|

AD 10 |

48 |

GND |

GND |

76 |

AD 52 |

|

GND/M66EN1 |

49 |

AD 9 |

AD51 |

77 |

AD 50 |

|

Ряд В |

N" |

РЯДА |

Ряд В |

Ntf |

РЯДА |

|

AD 49 |

78 |

GND |

AD 37 |

87 |

GND |

|

+VI/0 |

79 |

AD 48 |

+VI/0 |

88 |

AD 36 |

|

AD 47 |

80 |

AD 46 |

AD 35 |

89 |

AD 34 |

|

AD 45 |

81 |

GND |

AD 33 |

90 |

GND |

|

GND |

82 |

AD 44 |

GND |

91 |

AD 32 |

|

AD 43 |

83 |

AD 42 |

Reserved |

92 |

Reserved |

|

AD 41 |

84 |

+VI/0 |

Reserved |

93 |

GND |

|

GND |

85 |

AD 40 |

GND |

94 |

Reserved |

|

AD 39 |

86 |

AD 38 |

Конец 64-битного разъема |

||

' Сигнал M66EN определен в PCI 2.1.

|

Сигнал |

Назначение |

|

AD[31:0] |

Address/Data - мультиплексированная шина адре- |

|

C/BE[3:0]# |

Command/Byte Enable - команда/разрешение обра- |

|

FRAME* |

Кадр. Введением сигнала отмечается начало тран- |

|

DEVSEL# |

Device Select - устройство выбрано (ответ ЦУ |

|

IRDY# |

Initiator Ready - готовность И У к обмену данными |

|

TRDY# |

Target Ready - готовность ЦУ к обмену данными |

|

STOP# |

Запрос ЦУ к ИУ на останов текущей транзакции |

|

LOCK# |

Используется для установки, обслуживания |

|

REQ# |

Request - запрос от PCI-мастера на захват шины |

|

GNT# |

Grant - предоставление мастеру управления шиной |

|

PAR |

Parity - общий бит паритета для линий AD[31:0] |

|

Сигнал |

Назначение |

|

PERR# |

ParityError - сигнал об ошибке паритета (от устрой- |

|

PRSNT[1,2]# |

Present - индикаторы присутствия платы, коди- |

|

RSTft |

Reset - сброс всех регистров в начальное состояние |

|

IDSEL# |

Initialization Device Select - выбор устройства в циклах |

|

SERR |

System Error - системная ошибка. Активизируется |

|

REQ64# |

Request 64 bit - запрос на 64-битный обмен |

|

ACK64# |

Подтверждение 64-битного обмена |

|

INTRA# |

Interrupt А, В, С, D - линии запросов прерывания. |

|

CLK |

Clock - тактовая частота шины. Должна быть |

|

M66EN |

66MHzEriable - разрешение частоты синхронизации |

|

SDONE |

Snoop Done - сигнал завершенности цикла слежения |

|

SBO# |

Snoop Backoff - попадание текущего обращения к |

|

TCK |

Test Clock - синхронизация тестового интерфейса |

|

TDI |

Test Data Input - входные данные тестового |

|

TDO |

Test Data Output - выходные данные тестового |

|

TMS |

Test Mode Select - выбор режима для тестового |

|

TRST |

Test Logic Reset - сброс тестовой логики |

Одной из особенностей шины PCI является возможность

обмена данными между процессором и памятью одновремен-

но с обменом между другими устройствами PCI - Concurrent

PCI Transferring. Эта возможность реализуется не всеми чип-

сетами (в описаниях она всегда специально подчеркивает-

ся), а обь1чными устройствами (видеокарты и контроллеры

дисков) используется редко.

С мостами PCI/ISA связано понятие VGA Palette Snooping,

которое обеспечивает исключение из правила однозначной

маршрутизации обращений. Графическая карта в компью-

тере с шиной PCI обычно устанавливается на шину PCI. На

VGA-карте имеются регистры палитр (Palette Registers), при-

писанные к пространству ввода/вывода. Если графическая

система содержит еще и карту смешивания сигналов графи-

ческого адаптера с сигналом "живого видео", перехватывая

двоичную информацию о цвете текущего пиксела по шине

VESA Feature Connector (снимаемую до регистра палитр),

цветовая гамма будет определяться регистром палитр, раз-

мещенным на этой дополнительной карте. Возникает ситуа-

ция, когда операция записи в регистр палитр должна отра-

батываться одновременно и в графическом адаптере (на шине

PCI), и в карте видеорасширения, которая часто размещает-

ся на шине ISA. В BIOS Setup может присутствовать опция

PCI VGA Palette Snoop. При ее разрешении запись в порты

ввода/вывода по адресу регистра палитр будет вызывать

транзакцию как на шине PCI, так и на шине ISA, чтение же

по этим адресам будет выполняться только PCI. Реализа-

ция может возлагаться на графическую карту PCI. Для это-

го она во время записи в регистр палитр фиксирует данные,

но сигналы квитирования DEVSEL# и TRDY# не вырабаты-

вает, в результате чего мост распространяет этот неопознан-

ный запрос на шину ISA. В других реализациях мосту явно

указывают на данное исключение, и он сам распространяет

запись в регистры палитр на шину ISA.

Автоконфигурирование устройств (выбор адресов и преры-

ваний) поддерживается средствами BIOS и ориентировано

на технологию Plug and Play. Стандарт PCI определяет для

каждого слота конфигурационное пространство размером

до 256 8-битных регистров, не приписанных ни к простран-

ству памяти, ни к пространству ввода/вывода. Доступ к ним

осуществляется по специальным циклам шины Configuration

Read и Configuration Write, вырабатываемым контроллером

при обращении процессора к регистрам контроллера шины

PCI, расположенным в его пространстве ввода/вывода. После

аппаратного сброса (или по включении питания) устройства

PCI не отвечают на обращения к пространству памяти и вво-

да/вывода, они доступны только для операций конфигура-

ционного считывания и записи. В этих операциях устрой-

ства"'выбираются по индивидуальным сигналам IDSEL# и

сообщают о потребностях в ресурсах и возможных диапазо-

нах памяти. После распределения ресурсов, выполняемого

программой конфигурирования (во время POST), в устрой-

ства записываются параметры конфигурирования. Только

после этого к устройствам становится возможным доступ по

командам обращения к памяти и портам ввода/вывода.

Для ПЗУ расширения BIOS, установленных на картах PCI,

принят стандарт, несколько отличающийся от традицион-

ных дополнительных модулей ROM BIOS. Поскольку шина

PCI используется не только в PC, в ПЗУ карты может хра-

ниться несколько модулей. Тип платформы (процессора)

указывается в заголовке модуля, и при инициализации

BIOS активизируется нужный. Такой механизм позволяет,

например, один и тот же графический адаптер устанавли-

вать и в IBM PC, и в Power PC.

В состав шины PCI введены сигналы для тестирования адап-

теров по интерфейсу JTAG. На системной плате эти сигналы

задействованы не всегда, но они могут и организовывать ло-

гическую цепочку тестируемых адаптеров.

Некоторые фирмы выпускают для PCI карты-прототипы, но

доукомплектовать их адаптером собственной разработки

сложнее, чем карту ISA. Здесь сказываются сложные прото-

колы и высокие частоты.

Слот PCI достаточен для подключения адаптера (в отличие

от VLB), на системной плате он может сосуществовать с

любой из шин ввода/вывода и даже с VLB. На некоторых

системных платах позади одного из слотов PCI имеется

разъем Media Bus, на который выводятся сигналы ISA. Он

используется для размещения на графическом адаптере PCI

звукового чипсета, предназначенного для шины ISA.

Для устройств промышленного назначения в начале 1995 г.

был принят стандарт Compact PCI. Шина Compact PCI (сРСГ)

разрабатывалась на основе спецификации PCI 2.1. Эта шина

отличается большим количеством поддерживаемых слотов:

8 против 4. Появились новые 4 пары сигналов запросов и

предоставления управления шиной. Шина поддерживает

32-битный и 64-битный обмен (с индивидуальным разреше-

нием байт). При частоте шины 33 МГц максимальная про-

пускная способность составляет 133 Мбайт/с для 32 бит и

266 Мбайт/с для 64 бит (в середине пакетного цикла). Воз-

можна работа на частоте 66 МГц. Шина поддерживает спе-

цификацию РпР. Кроме того, в шине возможно применение

географической адресации, при этом адрес модуля (на кото-

рый он отзывается при программном обращении) определя-

ется его положением в каркасе. Для этого на коннекторе J1

имеются контакты GAO...GA4, коммутацией которых на "зем-

лю" для каждого слота задается его двоичный адрес. Геогра-

фическая адресация позволяет переставлять однотипные мо-

дули, не заботясь о конфигурировании их адресов (хорошая

альтернатива системе РпР - модуль "встанет" всегда в одни

и те же адреса, которые без физического вмешательства боль-

ше не изменятся). Конструктивно платы Compact PCI пред-

ставляют собой еврокарты высотой 3U (100х160 мм) с одним

коннектором (J1) или 6U (233х160 мм) с двумя кон-

некторами (J1 nJ2). Коннекторы - 7-рядные штырьковые

разъемы с шагом 2 мм между контактами, на кросс-плате -

вилка, на модулях - розетки. Контакты коннекторов имеют

разную длину: более длинные контакты цепей питания при

установке модуля соединяются раньше, а при вынимании

разъединяются позже, чем сигнальные. Такое решение по-

зволяет производить "горячую" замену модулей. Собствен-

но шина использует только один коннектор (J1), причем

в 32-битном варианте не полностью - часть контактов мо-

жет задействовать пользователь, 64-битная шина использу-

ет коннектор полностью. Одно посадочное место на кросс-

плате резервируется под контроллер шины, на который

возлагаются функции арбитража и синхронизации. На его

коннекторе шиной используется большее число контактов,

чем на остальных. У больших плат коннектор J2 предостав-

ляется пользователю, а между коннекторами J 1 и J2 может

устанавливаться 95-контактный коннектор J3. Конструкция

коннекторов позволяет для J2 применять специфические мо-

дификации (например, с разделяющим экраном и механи-

ческими ключами). В шине предусматривается наличие не-

зависимых источников питания +5 В, +3,3 В и ±12 В.

На базе шины Compact PCI фирмой National Instruments раз-

работана спецификация PXI (PCI extensions for Instrumenta-

tion - расширение PCI для инструментальных систем) в тех

же конструктивах. В шине PXI часть контактов, определенных

в Compact PCI как свободно используемые, предназначается

для дополнительных шин. Шина Trigger Bus (8 линий) звез-

дообразно соединяет слот своего контроллера (первый после

системного контроллера PCI) с остальными слотами. Шина

позволяет осуществлять синхронизацию разных модулей, что

зачастую требуется в измерительных системах. Для прецизи-

онной синхронизации имеется сигнал опорной частоты 10 МГц

PXI_CLK, который звездообразно (с одинаковыми задержка-

ми распространения сигнала) разводится по слотам. В PXI

определены локальные шины, предназначенные для связи со-

седних пар слотов. Каждая локальная шина имеет 13 линий,

которые могут использоваться как для цифровых, так и для

аналоговых (до 48 В) сигналов. Локальные шины объединя-

ют смежные слоты попарно (исключая слот системного кон-

троллера), образуя цепочку. Кроме механических и электри-

ческих характеристик PXI определяет ПО модулей: основной

ОС считается Windows NT/95, и модули должны поставляться

с соответствующими драйверами. Это экономит время, необ-

ходимое для системной интеграции. Модули PXI совмести-

мы с шиной Compact PCI, и модули Compact PCI - с шиной

PXI. Однако все преимущества спецификации реализуются

только при установке модулей PXI в шину PXI.

4.5. Магистральный интерфейс AGP

В настоящее время самой быстрой универсальной шиной рас-

ширения является PCI, имеющая при тактовой частоте

66 МГц и разрядности 32 бит пиковую пропускную способ-

ность 264 Мбайт/с. Одним из главных потребителей про-

пускной способности шины является графический адаптер.

По мере увеличения разрешения и глубины цвета требова-

ния к пропускной способности шины, связывающей дис-

плейный адаптер с памятью и центральным процессором

компьютера, повышаются. Одно из решений состоит в умень-

шении потока графических данных, передаваемых по шине.

Для этого графические платы снабжают акселераторами и

увеличивают объем видеопамяти, которой пользуется ак-

селератор при выполнении построений. В результате поток

данных в основном циркулирует внутри графической карты,

слабо нагружая внешнюю шину. Однако при трехмерных

построениях акселератору становится тесно в ограниченном

объеме видеопамяти, и его поток данных снова выплескива-

ется на внешнюю шину.

Фирма Intel на базе шины PCI 2.1 разработала новый стан-

дарт подключения графических адаптеров - AGP (Accelerated

Graphic Port - ускоренный графический порт). Этот порт

представляет собой 32-разрядную шину с тактовой частотой

66 МГц, по составу сигналов (табл. 4.8) напоминающую шину

PCI. Чипсет системной платы связывает AGP с памятью и

системной шиной процессора, не пересекаясь с "узким мес-

том" - шиной PCI. "Ускоренность" порта обеспечивается

следующими факторами:

йк конвейеризацией обращений к памяти;

^ сдвоенной передачей данных;

^ демультиплексированием шин адреса и данных.

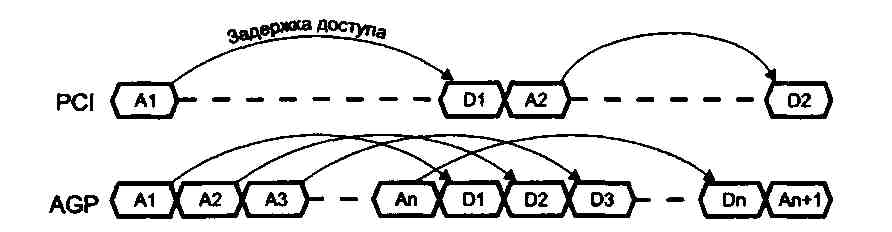

Конвейеризацию обращений к памяти иллюстрирует

рис. 4.11, где сравниваются обращения к памяти PCI и AGP.

В PCI во время реакции памяти на запрос шина простаи-

вает. Конвейерный доступ AGP позволяет в это время пе-

редавать следующие запросы, а потом получить поток от-

ветов. AGP предусматривает постановку в очередь до 256

запросов, но при конфигурировании по РпР реальные воз-

можности конкретной системы уточняются (возможности

контроллера памяти ограничены). AGP поддерживает две

пары очередей для операций записи и чтения из памяти с

высоким и низким приоритетами. В передачу данных лю-

бого запроса может вмешаться следующий запрос, в том

числе запрос в режиме PCI.

|

РЯДА |

№ |

Ряд В |

РЯДА |

№ |

Ряд В |

|

Spare |

1 |

12V |

Vddq3.3 |

34 |

Vddq3.3 |

|

5.0V |

2 |

Spare |

AD21 |

35 |

AD22 |

|

5.0V |

3 |

Reserved |

AD19 |

36 |

AD20 |

|

USB+ |

4 |

USB- |

GND |

37 |

GND |

|

GND |

5 |

GND |

AD17 |

38 |

AD18 |

|

INTB# |

6 |

INTA# |

C/BE2# |

39 |

AD16 |

|

CLK |

7 |

RST# |

Vddq3.3 |

40 |

Vddq3.3 |

|

RECW |

8 |

GNT# |

IRDY# |

41 |

FRAME# |

|

VCC3.3 |

9 |

VCC3.3 |

|

42 |

|

|

STO |

10 |

ST1 |

GND |

43 |

GND |

|

ST2 |

11 |

Reserved |

|

44 |

|

|

RBF# |

12 |

PIPE# |

VCC3.3 |

45 |

VCC3.3 |

|

GND |

13 |

GND |

DEVSEL# |

46 |

TRDY# |

|

Spare |

14 |

Spare |

Vddq3.3 |

47 |

STOP# |

|

SBAO |

15 |

SBA1 |

PERR# |

48 |

Spare |

|

VCC3.3 |

16 |

VCC3.3 |

GND |

49 |

GND |

|

SBA2 |

17 |

SBA3 |

SERR# |

50 |

PAR |

|

SBSTB |

18 |

Reserved |

C/BE1# |

51 |

AD15 |

|

GND |

19 |

GND |

Vddq3.3 |

52 |

Vddq3.3 |

|

SBA4 |

20 |

SBA5 |

AD14 |

53 |

AD13 |

|

SBA6 |

21 |

SBA7 |

AD12 |

54 |

AD11 |

|

KEY |

22 |

KEY |

GND |

55 |

GND |

|

KEY |

23 |

KEY |

AD10 |

56 |

AD9 |

|

KEY |

24 |

KEY |

AD8 |

57 |

C/BEO# |

|

KEY |

25 |

KEY |

Vddq3.3 |

58 |

Vddq3.3 |

|

AD31 |

26 |

AD30 |

ADSTBO |

59 |

Reserved |

|

AD29 |

27 |

AD28 |

AD7 |

60 |

AD6 |

|

VCC3.3 |

28 |

VCC3.3 |

GND |

61 |

GND |

|

AD27 |

29 |

AD26 |

ADS |

62 |

AD4 |

|

AD25 |

30 |

AD24 |

AD3 |

63 |

AD2 |

|

GND |

31 |

GND |

Vddq3.3 |

64 |

Vddq3.3 |

|

ADSTB1 |

32 |

Reserved |

AD1 |

65 |

ADO |

|

AD23 |

33 |

C/BE3# |

SMBO |

66 |

SMB1 |

4.5. Магистральный интерфейс AG P 171

Рис. 4.11. Циклы обращения к памяти РС1 и AGP

Сдвоенная передача данных обеспечивает при частоте 66 МГц

пропускную способность до 532 Мбайт/с, что для 32-битной

шины неожиданно. В AGP кроме "классического" режима,

называемого теперь "х1", в котором за один такт синхрони-

зации передается один 4-байтный блок данных, есть режим

".г2", когда блоки данных передаются как по фронту, так и

по спаду сигнала синхронизации (как в АТА Ultra DMA).

Управление передачей в таком режиме названо Sideband

Control (приставка SB к имени сигнала). Заказать режим х2

может только графическая карта, если она его поддержива-

ет. При переходе на тактовую частоту 100 МГц пропускная

способность повышается до 800 Мбайт/с.

Демультиплексирование (разделение) шины адреса и данных

сделано несколько необычным образом. Демультиплексиро-

вание подразумевает наличие двух полноразрядных шин -

адреса и данных. Однако такой вариант дорог. Поэтому шину

адреса в демультиплексированием режиме AGP представля-

ют 8 линий SBA (Sideband Address), по которым за три так-

та синхронизации передаются четыре байта адреса, длина за-

проса (1 байт) и команда (1 байт). За каждый такт

передаются по два байта - один по фронту, другой по спаду

тактового сигнала. Поддержка демультиплексированной

адресации не является обязательной для карты AGP. Требу-

ется также поддержка хост-контроллера. Альтернативным

способом подачи адреса является обычный - по мультиплек-

сированной шине AD.

AGP может реализовать всю пропускную способность 64-бит-

ной системы памяти компьютера на процессорах Pentium и

выше. При этом возможны конкурирующие обращения к

памяти как со стороны процессора, так и со стороны мостов

шин PCI.

Порт AGP может работать как в своем "естественном" ре-

жиме с конвейеризацией и сдвоенными передачами, так и в

режиме шины PCI. В конвейеризированном режиме, в кото-

ром начало цикла отмечается сигналом Р1РЕ#, возможны

только обращения к памяти. В режиме PCI циклы начина-

ются с сигнала FRAME#, и обращения возможны как к про-

странству памяти, так и к пространству ввода/вывода и кон-

фигурационному пространству. Кроме собственно AGP, в

порте AGP заложены сигналы шины USB, которую предпо-

лагается заводить в монитор. Внешне карты с портом AGP

похожи на PCI, но у них используется разъем повышенной

плотности с "двухэтажным" (как у EISA) расположением

ламелей. Сам разъем располагается дальше от задней кром-

ки платы, чем разъем PCI.

Фирма Intel ввела поддержку AGP в чипсеты для процессо-